-

近年来随着核物理实验技术的高速发展,需要利用加速到各种不同能量的离子轰击原子核来研究核结构和运动变化规律[1]。粒子物理和核物理实验的能量越来越高,探测器的规模越来越大,实验产生的数据量也是越来越多,要求在实验时,能够及时地把实验数据传输并且记录下来。传统电子学读出系统的设计方法面临着巨大的挑战,未来的探测器读出系统必然向大规模、高密度、高速度的趋势发展。目前,欧洲的强子对撞机LHC(Large Hadron Collider)将CMS(Compact Muon Solenoid)探测器的数据传输系统由VME架构升级为MicroTCA(Micro Telecom Computing Architecture)架构[2],但是国内的数据传输系统升级较为缓慢,北京正负电子对撞机(BEPC)依然采用VME架构[3],兰州重离子加速器(HIRFL)采用的是PXI架构[4],这些架构的数据传输都是依赖于并行总线进行传输的。由于并行总线是多个数据同时进行传输,需要考虑到数据的协同问题,所以无法不断提升并行传输的频率或者说提升的难度会越来越大[5]。相对应的串行总线只有一条传输链路,就可以不断地提升传输的速率,只要速度提高了就可以弥补一次只能传输一个数据的缺陷。

为了满足核物理实验的传输速度要求,本文基于MicroTCA(Micro Telecom Computing Architecture)架构设计了一种新型先进的数据传输系统AMC信号处理卡。该AMC信号处理卡采用MicroTCA架构,体积小、成本低。各个板卡作为各自的功能模块可以进行单独的设计,易于开发和维护,又可以根据核物理实验的需求进行不断的升级等,具有很多优点[6]。该板卡最突出的特点是采用了高速串行总线PCIe作为系统背板总线,串行总线在速度提升方面有着巨大的优势,符合核物理实验发展迅速的特点。

-

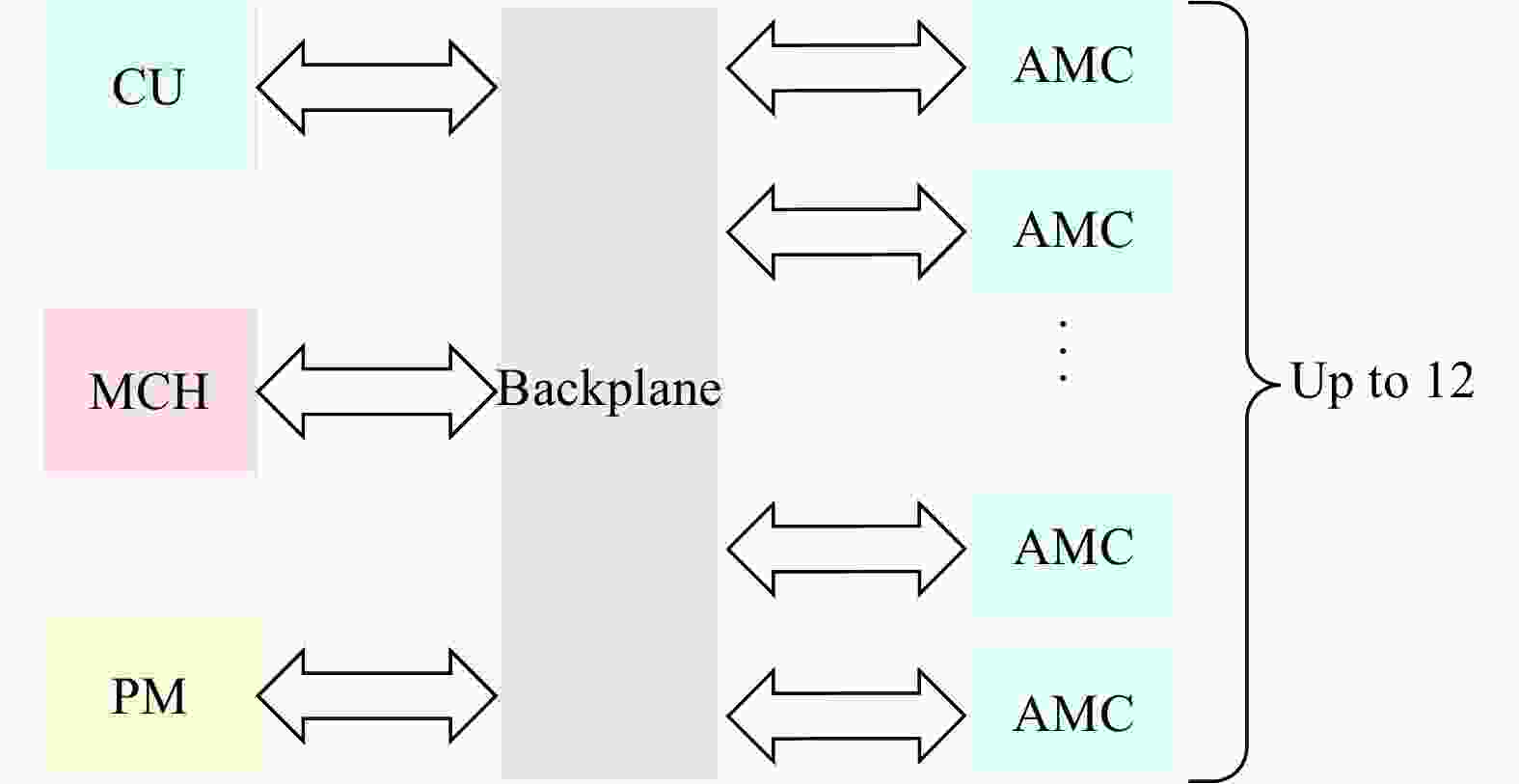

该AMC信号处理卡是基于MicroTCA平台来设计的。在2002年出现了一种先进的通信架构ATCA(Advanced Telecom Computing Architecture),取代了传统架构。这种架构采用了模块化结构,比传统的架构具有更好的兼容性和可扩展性,以及更加完善的系统管理机制,在通信领域发挥了不可替代的作用。但是这种结构却同样有着不少的缺点,例如,成本高、系统规模繁杂、体积大等缺点[7],使得ATCA架构只能适用于大型的系统,而不受中小型等低端市场的青睐。因此在2006年出现了对中小型系统更加友好的系统架构--MicroTCA架构。MicroTCA架构是在ATCA的基础上进行简化改进的,保留继承了ATCA架构模块化、高带宽、高集成度的优势,另一边在规模复杂度、体积和成本上面进行了缩减,使得该系统变得适合中小型系统的使用[8]。MicroTCA平台主要由高级夹层板卡(AMC)、载板中枢(MicroTCA Carrier Hub, MCH)、电源模块(Power Module, PM)、互联背板(backplane)、冷却单元(Cooling Unit, CU)等5部分组成,如图1所示。

-

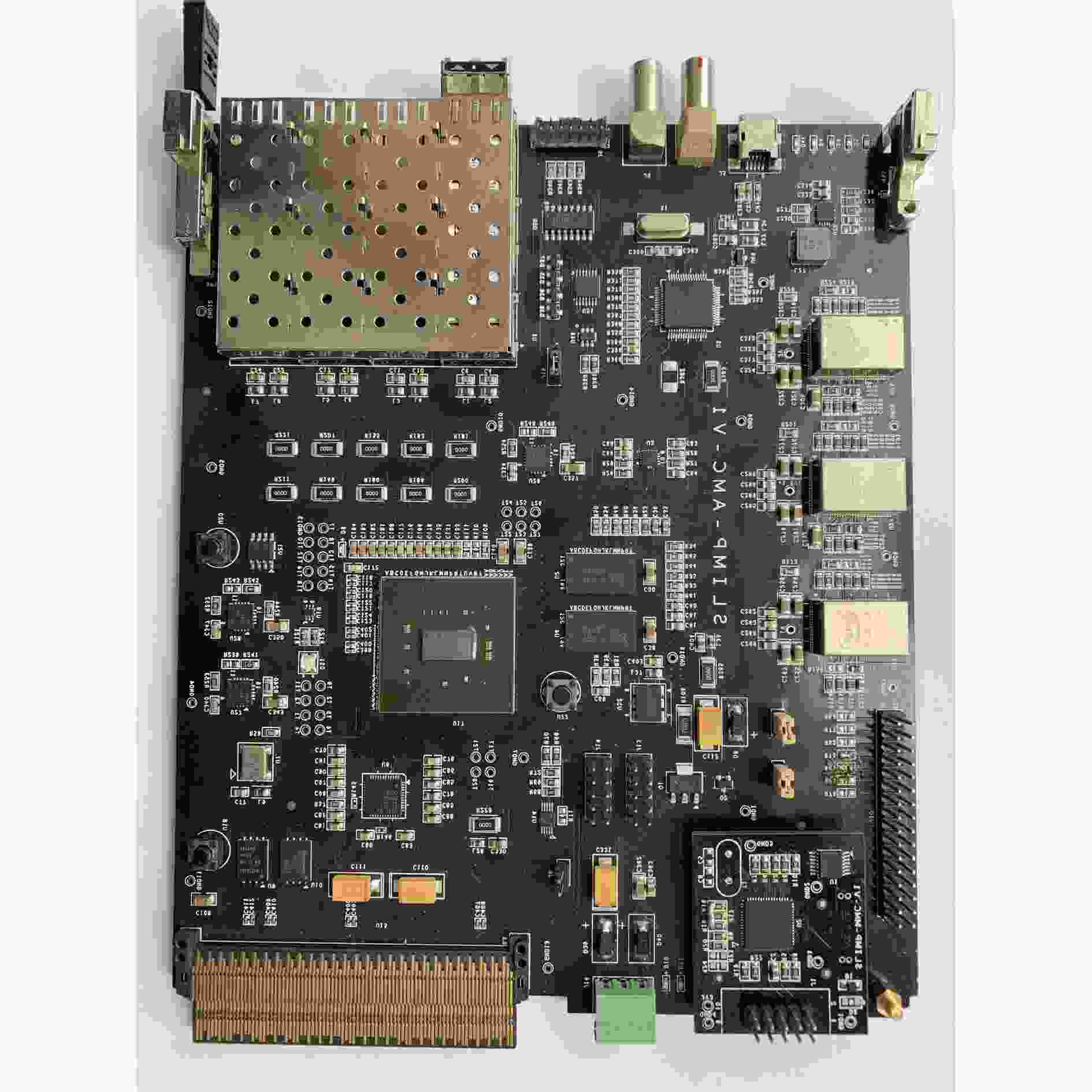

该电路原理框图如图2所示,该电路采用Xilinx公司的Kintex7系列FPGA为主芯片,4个DDR3、1个QSPI FLASH、一些外设接口和时钟同步电路组成。该AMC信号处理卡实物图如图3所示,外围接口主要包含1个AMC背板金手指接口、4路10 Gbps光纤SFP+接口。板上载有模块管理控制器MMC,MMC上实现基于IPMI的智能管理系统,根据IPMI协议标准,在MMC上设计实现IPMB(Intelligent Platform Management Bus)物理总线,建立IPMI指令的数据结构,合理规划指令接收、发送、执行的时序逻辑[9]。使之负责记录板卡的工作状态,并将结果通过IPMI上传给MCH,从而使MCH完成对AMC的上电激活、温度监控、电子密钥等功能。同时,MMC上的管理系统会实时地对AMC进行监控,确保AMC工作状态正常。该板卡可以实现与4个前端电子学电路模块的同时通信,可以用来完成事件的高速缓存、符合判选和事件的打包上传。

-

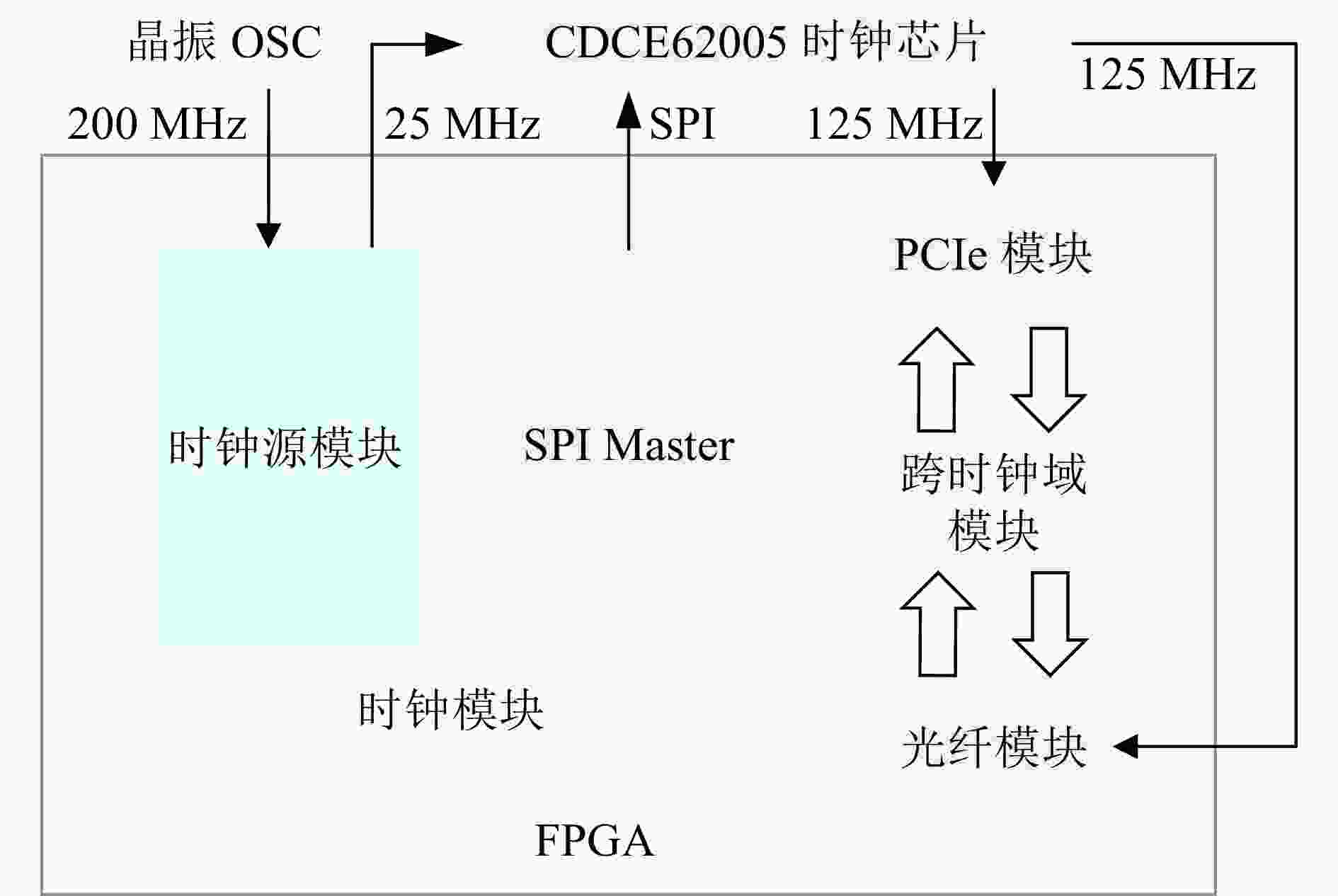

在高速串行传输模式下,PCIe模块和GTX模块对时钟的要求比较苛刻,需要给二者提供高质量、抖动小的差分时钟信号。AMC板卡上的FPGA的系统时钟由振荡器(SIT9102)提供一个200 MHz时钟,也可以通过LEMO差分端口从外部输入时钟。本系统的AMC板卡上还搭载了一个CDCE62005时钟芯片,通过SPI协议,负责给光纤模块和PCIe模块提供高精度的时钟。CDCE62005时钟芯片经过SPI协议配置,最多可以产生五对的差分时钟输出。本系统时钟的具体结构如图4所示,该系统在FPGA内部生成了一个时钟模块,时钟模块是用来初始化CDCE62005时钟芯片,先将晶振的200 MHz时钟分频到25 MHz,作为时钟芯片的时钟源,再通过SPI配置时钟芯片的寄存器,使时钟芯片产生两路差分时钟,分别给光纤模块提供125 MHz的参考时钟,给PCIe模块提供125 MHz基准时钟。

-

光纤模块的结构如图5所示,该模块也可以称为GTX收发器,主要可以分为三个部分:Gen、Check和Support。GTX是Xilinx针对高速串行传输提供的一个收发器IP[10],Gen模块是用来发送对齐码和数据的;Check是检查数据是否正确传输以及通过对齐码把数据对齐还原;Support是提供的IP核心代码,其中包括内部时钟模块、GT基础设置、复位模块以及IP核。该模块的数据收发的参考时钟都是125 MHz,系统时钟是100 MHz,收发的速率是5 Gbps,用户的接口数据宽度都是64位。该模块使用的是8B/10B的数据编码方式,K字符是8B/10B规范当中的对齐字符,使用的是K28.5对齐字符。在FPGA上电之后,光纤模块在没有收到上位机命令的情况下,将会一直发送一串对齐码,即在光纤没有发送有效数据的时候也一直让光纤链路的信号保持对齐状态,因为用户传输的数据不一定是符合字的边界,所以需要不断地进行对齐操作。

-

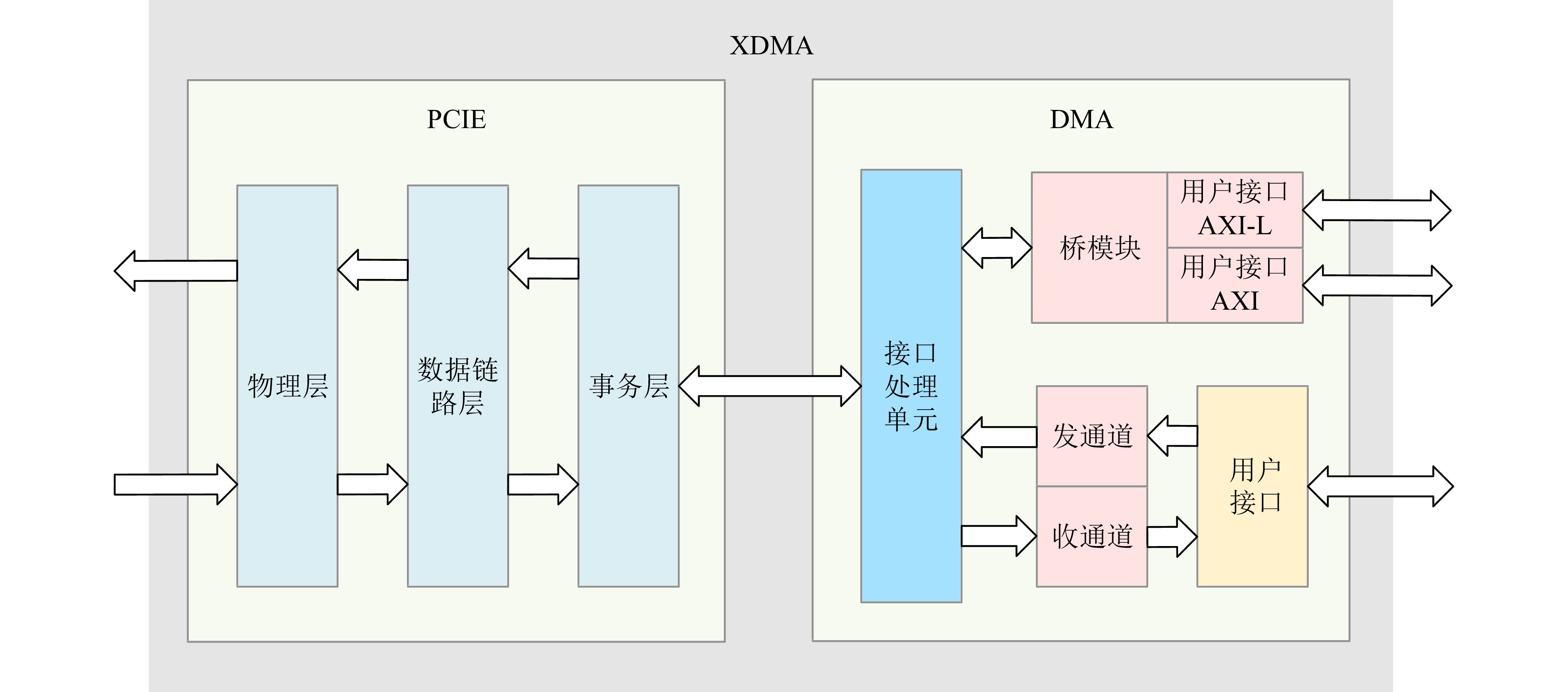

PCIe模块使用的是Xilinx提供的XDMA的IP核[11],该IP主要可以分为DMA模块和PCIe模块两部分,其结构如下图6所示。其中,PCIe模块支持PCIe2.0协议标准,每条通道的传输速度最高可达5 GT/s,是一种高可靠、高带宽、可伸缩串行互联的模块。该模块内部包含PCIe规范中的事务层、数据链路层和物理层。DMA模块实现了对PCIe中的数据包的信息处理,实现与用户接口的对接。在数据的接口上,XDMA提供了两条名为C2H(Card to Host)的写通道和两条名为H2C(Host to Card)的读通道,并且每个通道相互独立[9]。本次设计把传到PCIe时钟域的数据通过一个独立的写通道写入XDMA,然后等待上位机发起读数据请求,将XDMA上的数据读出,完成数据的传输。

该IP的PCIe部分是EP设备,使用100 MHz的参考时钟,使用×1的数据通道,通道的最大传输速度为5 GT/s。该IP的DMA部分使用的AXI-S作为DMA数据传输的用户接口,AXI的时钟频率是125 MHz,数据宽度和地址宽度都为64位。

-

误码率(Bit Error Rate, BER)作为高速数据传输技术的重要指标,它代表着数据传输的可靠性。对于数字通信系统,BER可以定义为出现误码的估计概率。误码率是通过系统传输一定比特的比特数和计算接收到的不正确的比特数来测量的,该测试是在实验室环境下测试AMC板卡光纤接口的稳定性和可靠性。我们使用Xilinx公司提供的IBERT IP核进行光纤传输接口误码率测试[12]。测试原理是通过收发器由外部回环进行自发自收而实现,即把同一组收发器的TX和RX进行短接,TX发送端通过发送某种特定序列的数据流,在RX接收端接收到数据后,进行比对发送和接收的数据,从而得出收发器误码的统计值。在测试中,我们使用8B/10B的编码方式并将速度设置在5 Gbps,测试方式为光纤自回环,将SFP模块的输出端口直接连接到输入端口,回环测试使用的是32位伪随机序列(PRBS-31),每两个小时记录一次数据,总共进行42个小时的误码率测试。如图7所示,在运行42 h之后,误码率为7.62×10−15。

-

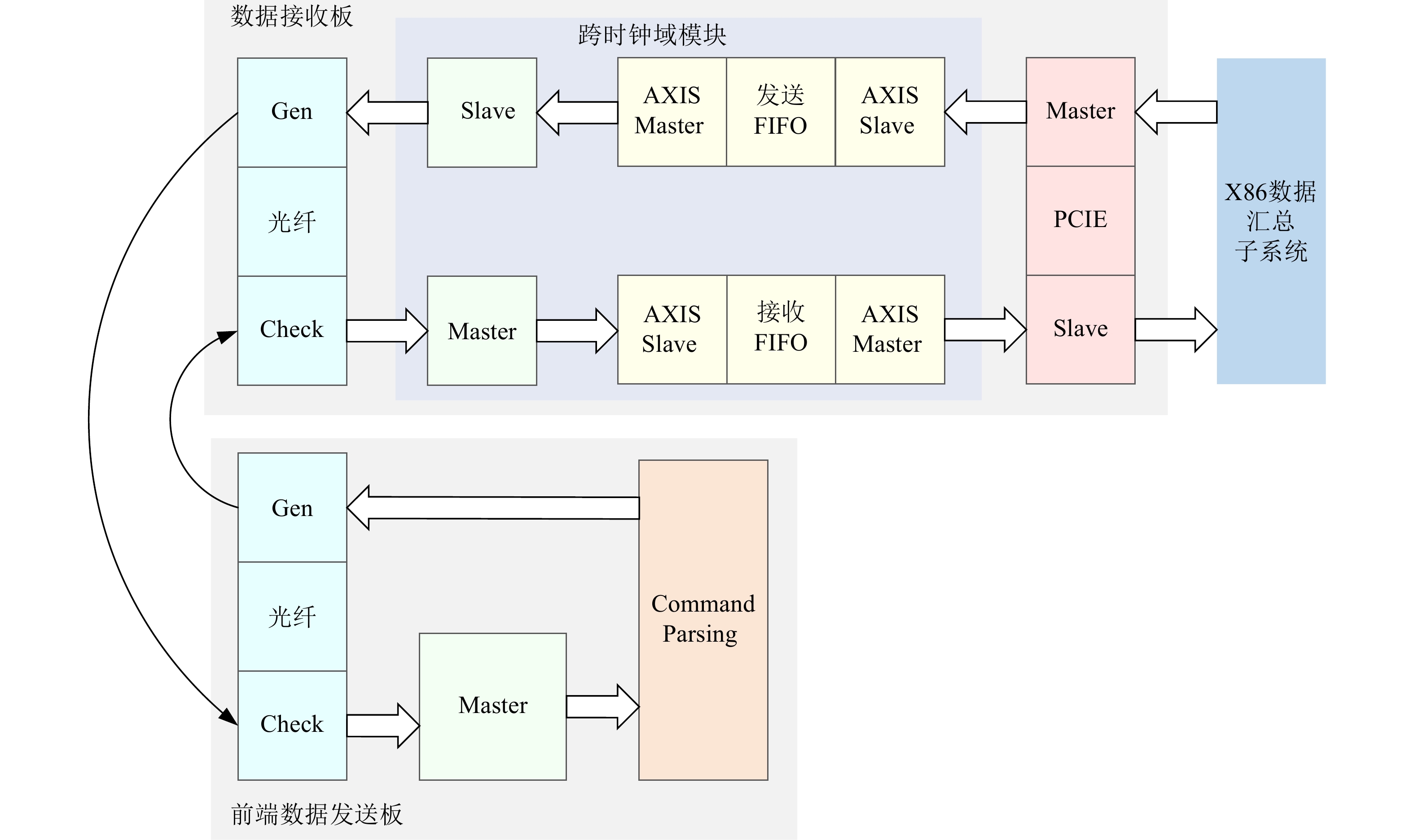

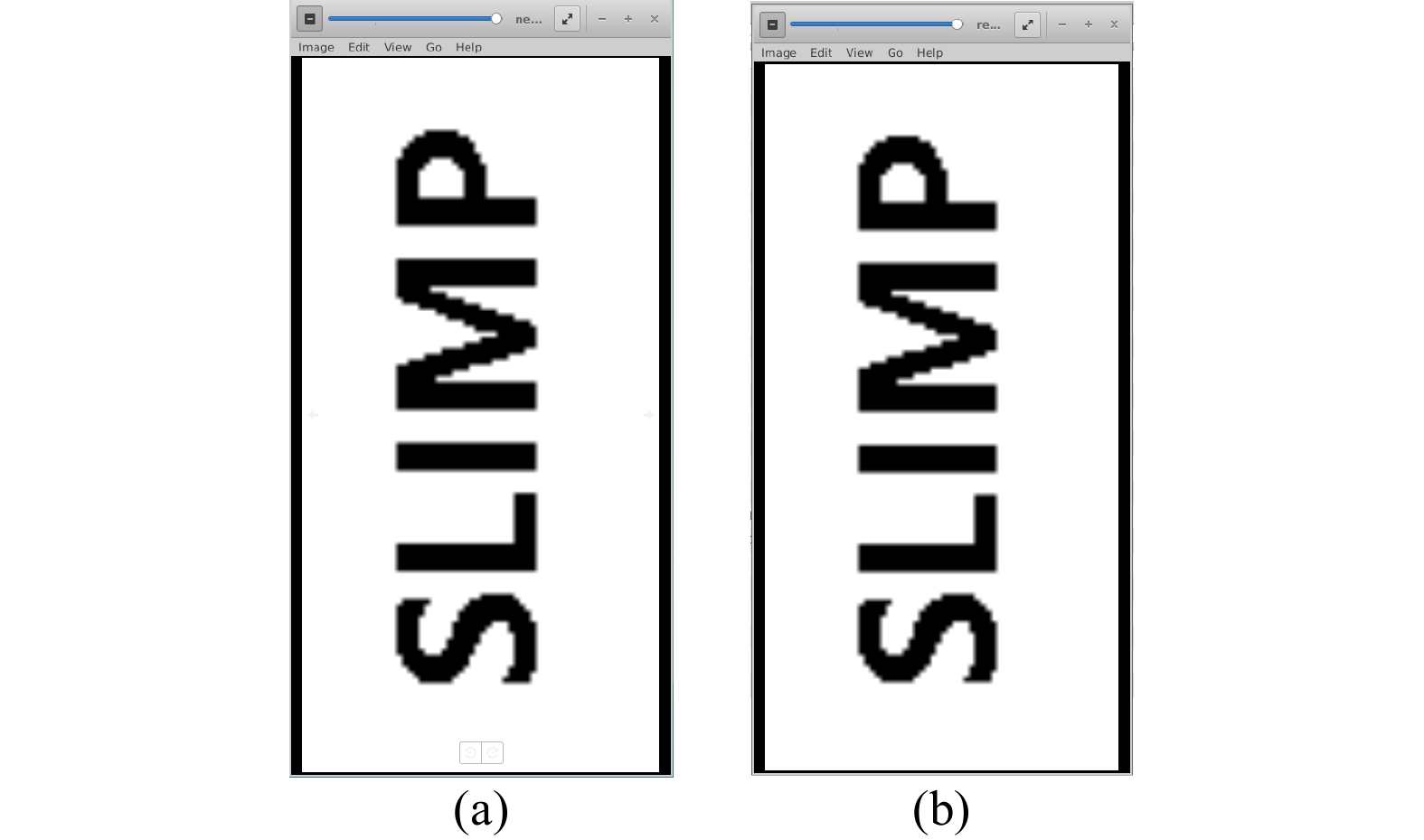

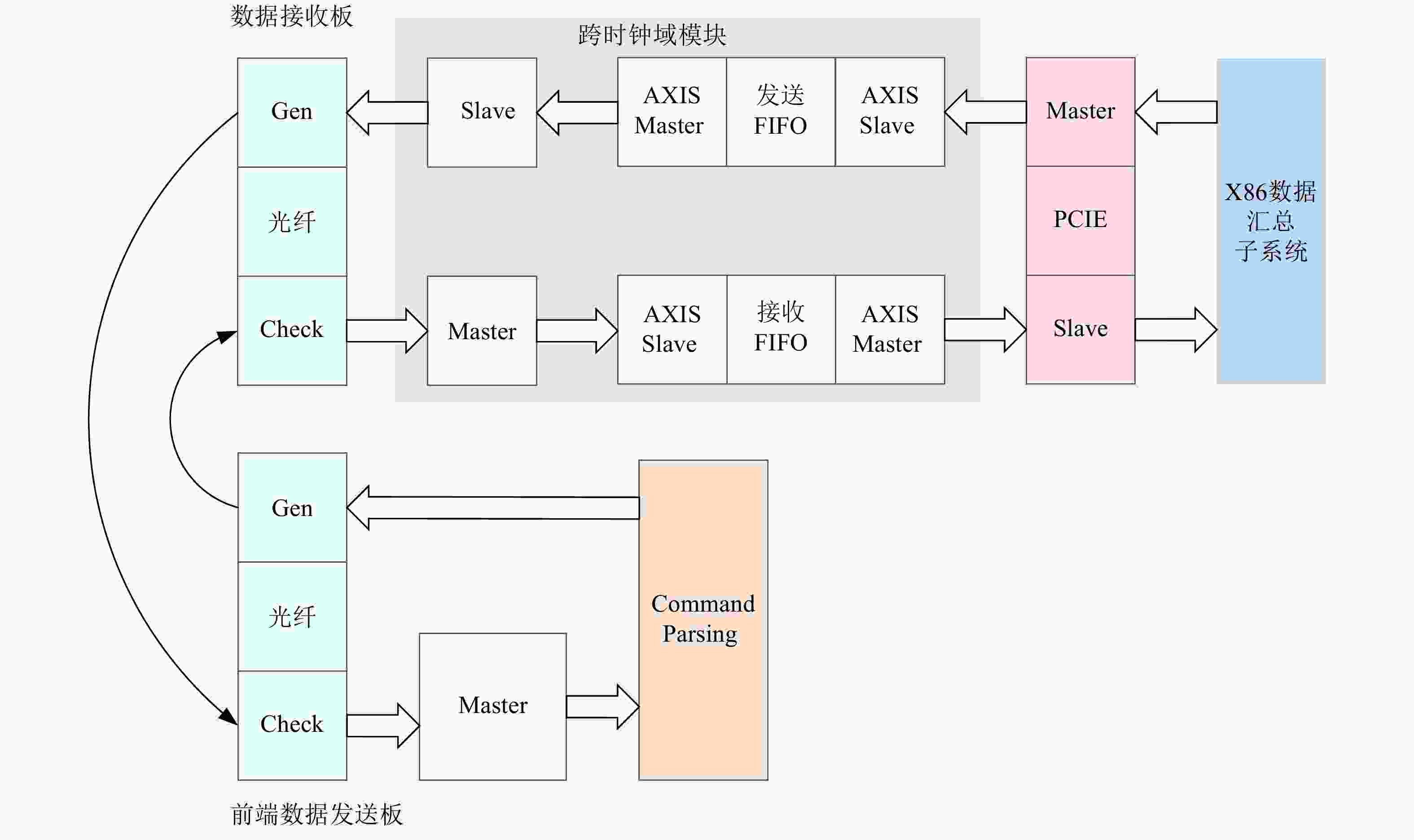

测试的目的是验证数据回环测试数据传输功能。写有SLIMP (像素探测器研究室)的字符的图片生成二进制数据后,按照如图8所示的流程进行回环测试,首先是上位机先发送命令通过PCIe传输至AMC信号处理卡,通过跨时钟域模块后传输给AMC信号处理卡的光纤模块,光纤输出后发送给前端电子学板,然后前端电子学接收到命令并解析完,在通过光纤口发送SLIMP图片的数据到AMC信号处理卡的光纤接收模块,然后通过跨时钟域模块给到PCIe,最后PCIe再传输至上位机保存。其中跨时钟域模块是用来进行数据的缓存,以及解决跨时钟域传输过程中遇到的时钟频率和数据位宽不匹配等问题。AMC信号处理卡接收到预期大小的数据信号之后,就发送命令要求前端电子学板停止发送数据。上位机会把数据接收并且存放在文件当中,最终把发送的数据译码成图片,如图9所示,通过原图片[图9(a)]和新生成的图片[图9(b)]对比,我们可以发现,两者完全一致。证明该系统的功能正常。

-

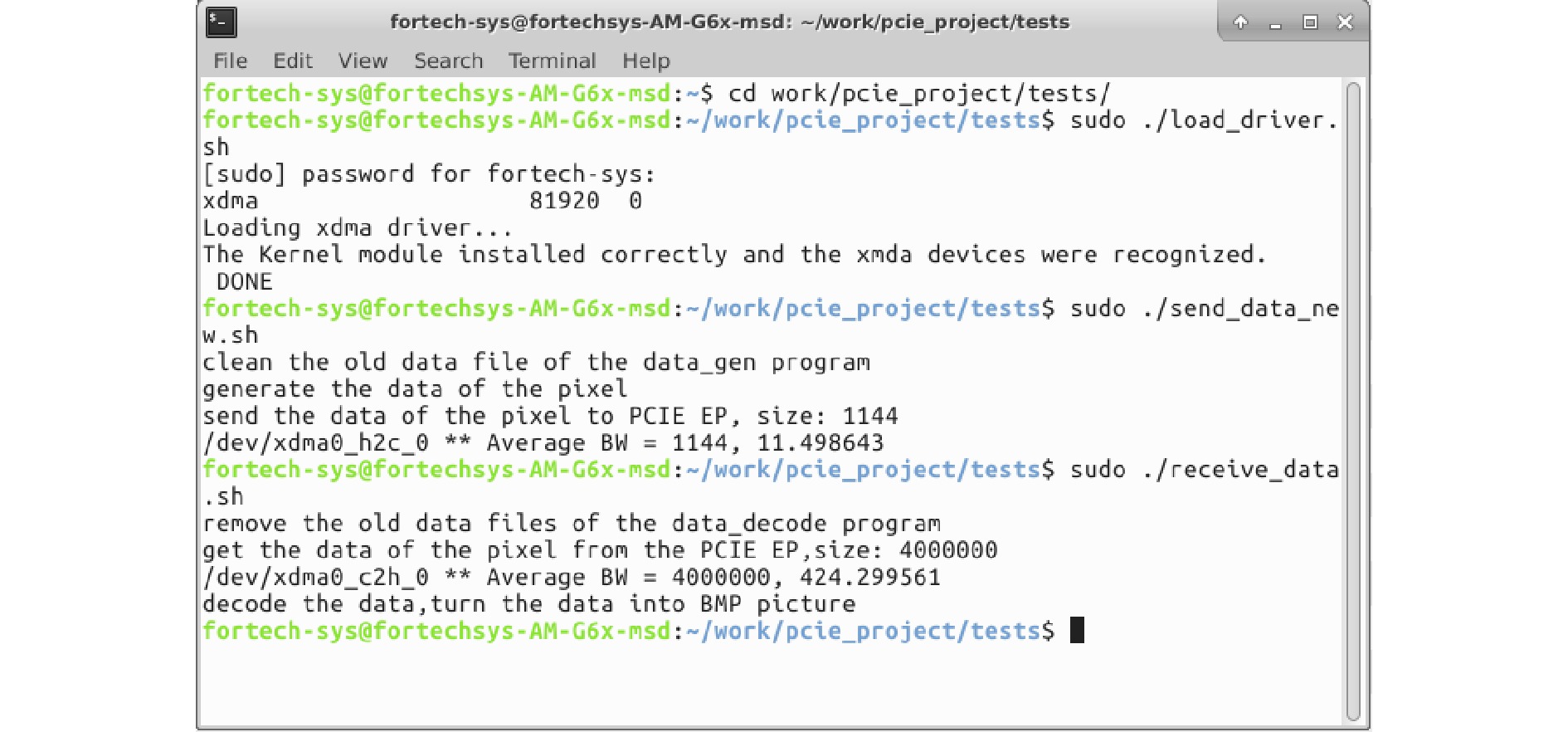

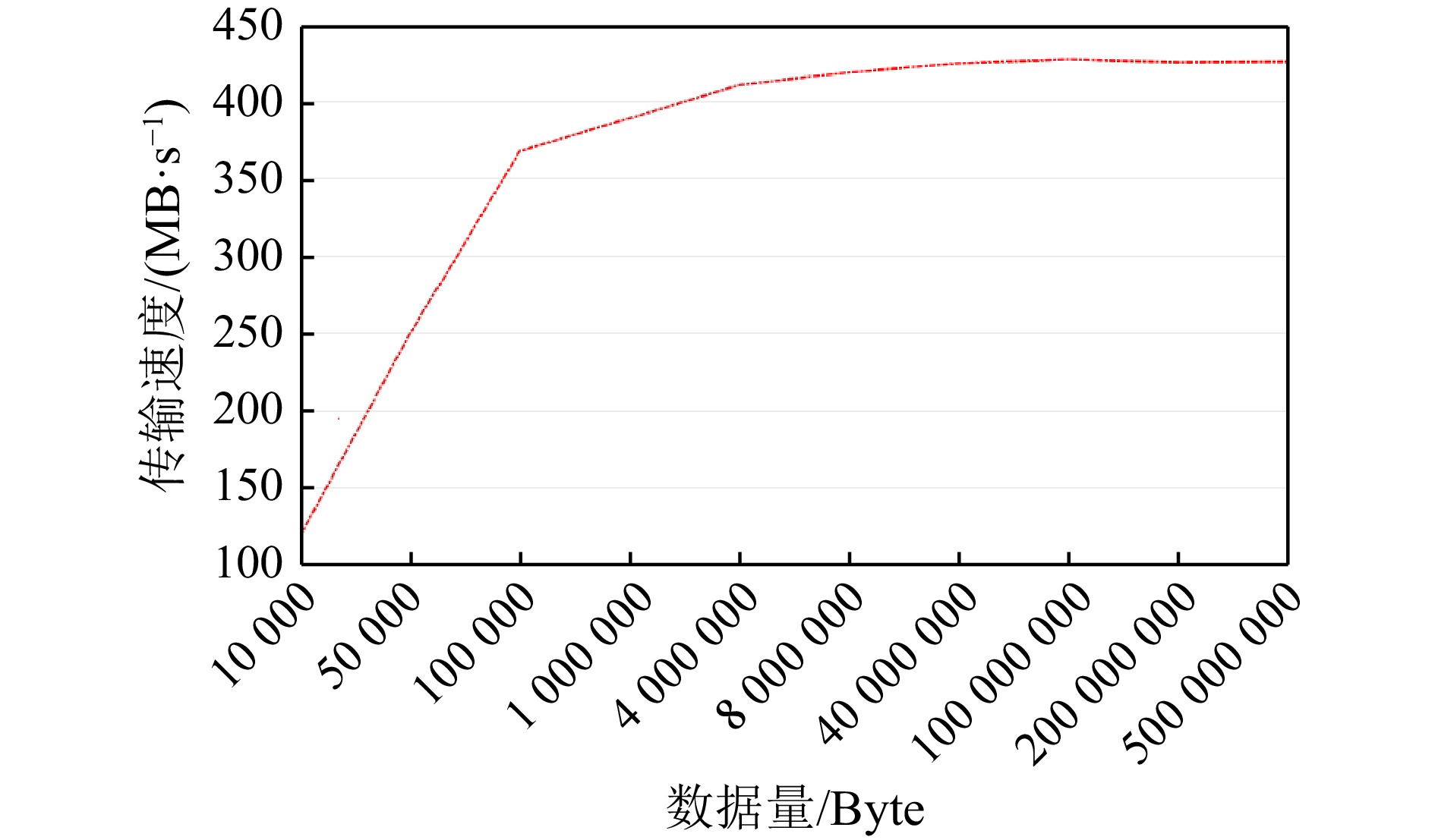

在验证完系统传输功能正常的同时,进一步对传输速率进行了测试。测试的是读速率,数据从光纤TX端发送到RX端,再发送到PCIe EP接收端,最后被PCIe RC读出。在速率测试当中,上位机先发送允许传输的命令,然后通过修改接收数据的大小,接收不同大小的数据。如图10所示,接收100 MByte大小的数据是通过接收25次4 MByte大小的数据来达到的,可以看到传输的速度大小是424.3 MB/s。在经过多次不同大小的数据量的传输速度测试,我们可以得到如图11所示的传输速度折线图。该图的横坐标为数据量,单位是Byte;纵坐标是传输速度,单位是MB/s。PCIe的物理层通信协议的速度可达5 GT/s,所以理论上的传输速度可以达到4 Gbps,即500 MB/s。光纤链路的传输速度约为5 Gbps,即625 MB/s。但是在传输的过程中不仅受限于硬件的运行时间还得考虑到软件的运行时间,因此传输的数据量越小的时候,这些额外的运行时间所占的比重就越大。伴随着传输的数据量不断增大,实际传输占用时间比重不断增加,因此传输的速度也就逐渐接近于速度极值。图11可以看到,该速度的极值大约在430 MB/s,接近PCIe链路的理论值。

-

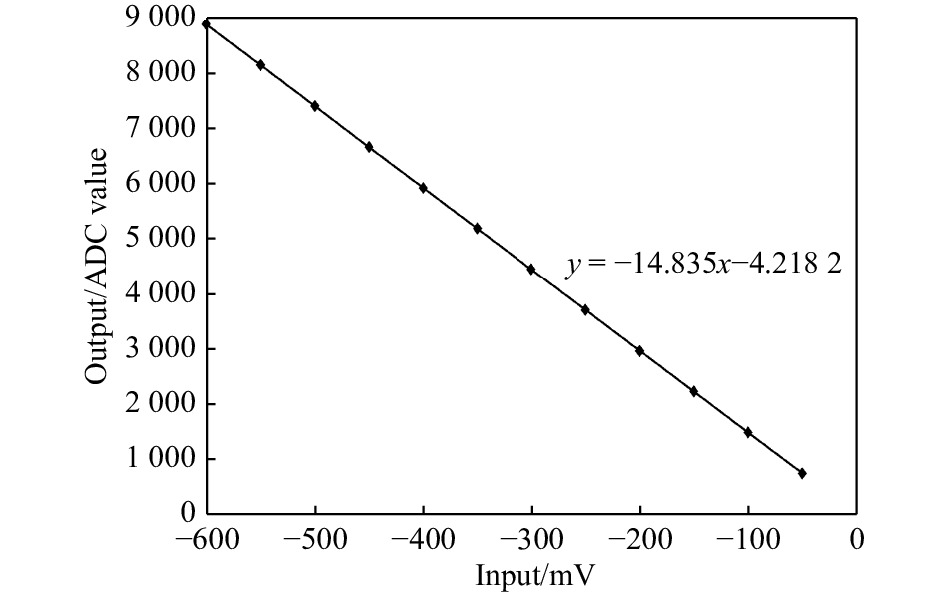

测试中将低温高密核物质测量谱仪(CSR External-target Experiment, CEE)分系统之一的零度角量能器(Zero Degree Calorimeter, ZDC)的前端电子学与该AMC信号处理卡进行了联合测试,ZDC前端电子学主要由模拟调理电路、ADC、FPGA及光纤接口组成,主要用来获取PMT输出的电荷信号[13]。在实验室环境下,用信号源输出负指数衰减信号到ZDC前端电子学的模拟信号输入通道,周期设置为5 μs,调节幅度从−600 ~ −50 mV变化,步进50 mV,共测试12个幅度点,每个幅值下前端电子学采集50万个事例数据,并把它们传输给MicroTCA平台上的AMC信号处理卡,再通过PCIe背板总线发送给上位机存储。最后用MATLAB软件进行数据分析和拟合,得到线性拟合的结果。如下图12给出通道一的线性测试测试结果。

-

MicroTCA架构,有着体积小、成本低的优势,各个子卡作为各自的功能模块可以进行单独的设计,易于开发和维护。本文主要基于MicroTCA架构设计了一种AMC信号处理卡,该AMC信号处理卡主要由FPGA、DDR3、QSPI FLASH、AMC背板金手指接口、光纤接口等组成。该AMC信号处理卡主要用来实现前端电子学系统数据的接收、缓存、在线处理和汇总。数据传输通过背板高速串行PCIe总线传输,传输速度是传统并行总线的数倍,并且有很强的开发潜力。通过测试验证,整个传输系统的链路传输功能正确。对信号处理卡具有较低的光纤误码率。另外,对整个系统的传输链路的读写速率进行了测试,该数据传输系统的带宽达到了430 MB/s,接近于理论极值,能够满足一般核物理实验的传输速率需求。

Design and Implementation of AMC Signal Processing Card Based on FPGA

doi: 10.11804/NuclPhysRev.40.2022076

- Received Date: 2022-07-06

- Rev Recd Date: 2022-08-10

- Publish Date: 2023-03-20

-

Key words:

- MicroTCA /

- AMC /

- high-speed serial bus /

- data transmission /

- bit error rate

Abstract: In the early stage, parallel bus architecture, such as VME and PXI bus, is widely used in the data transmission system of detector devices at home and abroad. However, with the development of nuclear physics experiments and the improvement of the speed of data transmission, the drawbacks of the difficulty in speeding up the parallel bus gradually appear. The data can not be transmitted through the backplane due to the low bus speed. In this paper, we design a new advanced data transmission Advanced Mezzanine Card(AMC) signal processing card based on Micro Telecom Computing Architecture(MicroTCA). A high-speed PCIe serial bus which has significant advantages in speed improvement is used in the backplane bus of the AMC signal processing card. The transmission function of the whole transmission link is tested and verified to be correct and the fiber error rate of the link transmission is lower than 7.62×10−15. The transmission speed is also close to the theoretical extreme, reaching 430 MB/s. Finally, the AMC signal processing card and front-end electronics are tested jointly, and the validity of the system is verified.

| Citation: | Honghui ZHANG, Haibo YANG, Liangrong LI, Shun LIAO, Honglin ZHANG, Xianqin LI, Zhen LI, Chengxin ZHAO. Design and Implementation of AMC Signal Processing Card Based on FPGA[J]. Nuclear Physics Review, 2023, 40(1): 86-91. doi: 10.11804/NuclPhysRev.40.2022076 |

甘公网安备 62010202000723号

甘公网安备 62010202000723号 DownLoad:

DownLoad: