-

采样率是波形数字化系统最重要的参数之一,并行交替采样(Time-Interleaved Analog-to-Digital Conversion, TIADC)技术通过采用多个ADC(Analog-to-Digital Converter)进行不同相位的并行采样,可成倍提升系统的等效采样率[1-7]。对于一个由M个ADC采样通道组成的TIADC系统,假设每个ADC的采样率为

$ {F}_{\mathrm{S}} $ ,采样周期为$ {T}_{\mathrm{S}} $ ,每个ADC的采样时间延迟$ {T}_{\mathrm{S}}/M $ ,则TIADC系统等效采样周期为$ {T}_{\mathrm{S}}/M $ ,等效采样率为$ M\times {F}_{\mathrm{S}} $ ,即系统采样率为单个ADC的M倍。动态性能是评估一个波形数字化系统性能的重要指标,由于TIADC系统各采样通道间失配误差的存在,其动态性能相对单个ADC会明显下降,故失配误差的修正是TIADC技术的一个研究重点。针对失配误差的修正,已有大量方法被提出并应用[8-14]。目前国际形势复杂,国外的超高速ADC使用受限,从这个角度考虑也需要发展自主化TIADC系统的设计。针对自主化TIADC技术及其失配误差修正技术研究的重要性,本课题组所在的实验室已设计了一套基于国产高速ADC的TIADC系统,并提出了一种基于完美重构算法的宽带失配误差修正方法[14]。为验证系统工作的正确性及修正方法的有效性,需进行测试与评估。

本工作首先简要介绍所测试的TIADC系统的结构,并简单介绍失配误差的概念及该算法的修正过程,然后对该系统的测试内容、各项测试的测试方法及测试平台的搭建进行详细介绍,最后给出上述各项测试内容的测试结果,并对测试结果进行分析。

-

本节首先对所测试的TIADC系统的结构进行简要介绍,然后介绍失配误差参数及其修正过程。

-

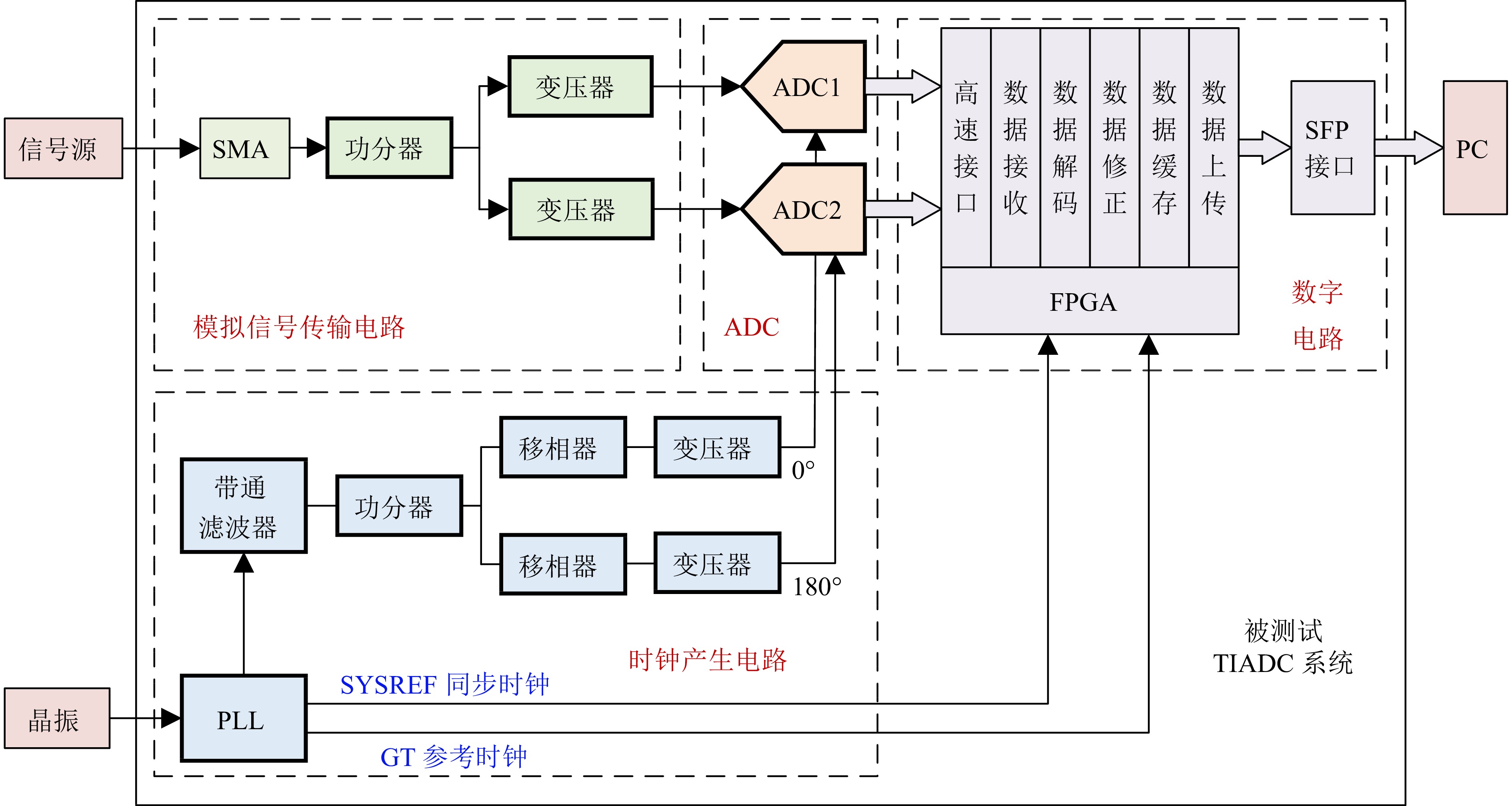

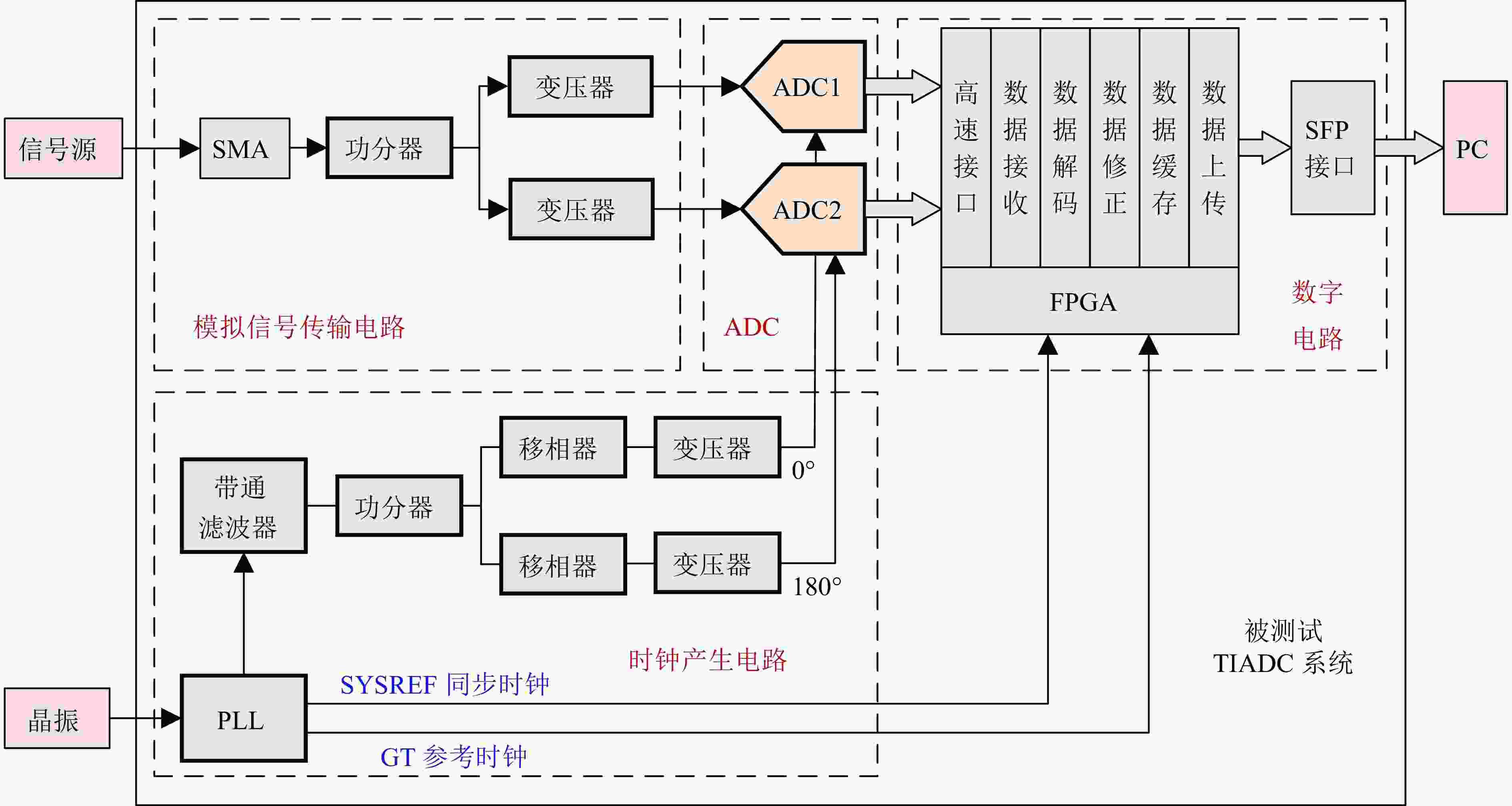

本工作所测试的5-Gsps 12-bit TIADC系统结构如图1所示。系统主要由模拟信号传输电路、时钟产生电路、ADC及数字电路四部分组成。

模拟信号传输电路包含SMA(SubMiniature version A)信号接口、功分器和两个变压器,外部信号源输出模拟信号,由SMA接口送入功分器,功分器将信号分为两路,两路单端信号各由一个变压器转换为差分信号,以适应ADC的差分输入。

时钟产生电路由锁相环(Phase Lock Loop, PLL)和采样时钟调理电路组成,外部晶振提供参考时钟,送入PLL。PLL一路输出为2.5 GHz时钟,经过带通滤波器、功分器、移相器及变压器转换为两路差分时钟送入2片ADC,完成采样时钟的生成、调理及发送;PLL另一路输出为数据同步及高速数据传输所需的特定频率的参考时钟。

ADC是本系统的关键,本系统使用2片2.5 Gsps 12 bit的国产高速ADC进行并行交替采样,其采样时钟相位分别为0°和180°,此工作状态下,系统采样时间间隔为200 ps,等效采样率5 Gsps。ADC通过符合JESD204B协议的高速串行数据接口输出。

数字电路包括FPGA(Field Programmable Gate Array)和SFP(Small Form Pluggable)数据接口,其中FPGA通过高速数据接口完成高速串行数据的接收、解码、修正、缓存,最终将数据通过SFP接口上传至PC(Personal Computer)。

-

在实际TIADC系统中,根据产生原因可将失配误差分为三种:增益误差、相位误差、偏置误差。

增益误差是由ADC自身增益的差异和模拟信号传输电路对信号幅度响应的差异而产生的,反映了各个采样通道采样信号的幅度不一致性,以第1通道为参考,第m通道的增益误差可表示为

$ {G}_{m} = {A}_{m}/{A}_{1} $ ,其中$ {A}_{m} $ 、$ {A}_{1} $ 分别表示第m通道和第1通道的信号幅度。相位误差是由实际采样时钟与理想采样时钟的偏差以及不同ADC对输入信号响应时间的不同而产生的,表征了实际采样时间的误差。在单个ADC采样周期为

$ {T}_{\mathrm{s}} $ 的M通道理想TIADC中,以第1通道为参考,其采样时间为$ {nT}_{\mathrm{s}} $ ,第m通道的采样时间应为$ n{T}_{\mathrm{s}}+\frac{m-1}{M}{T}_{\mathrm{s}} $ ,与第1通道的采样时间差为$ \frac{m-1}{M}{T}_{\mathrm{s}} $ 。实际的TIADC系统采样时间与理想情况存在一定偏差,第m通道的相位误差可表示为$ {\Delta t}_{m} = \frac{{t}_{m}-{t}_{1}}{{T}_{\mathrm{s}}/M} $ ,其中$ {t}_{m} $ 、$ {t}_{1} $ 分别表示第m通道和第1通道的实际采样时间。偏置误差是由各个ADC偏置的差异而产生的,反映了不同采样通道之间的直流(Direct Current, DC)偏置的不一致性。以第1通道为参考,第m通道的偏置误差可表示为

$\Delta o^{}_{m} = {o}^{}_{m}-{o}^{}_{1} $ ,其中${o}^{}_{m}$ 、${o}^{}_{1}$ 分别表示第m通道和第1通道的DC偏置。三种失配误差中,偏置误差一般只与采样率有关,可认为是一个不随输入信号频率变化的常量。而增益误差和相位误差与采样率和信号频率同时相关,采样率确定的系统以上两种失配误差随信号频率变化而变化,故失配误差修正中主要关注增益误差与相位误差的修正。

-

在本实验室之前的工作中,设计了一种基于完美重构算法的宽带内失配误差修正方法[14],该方法基于有限冲击响应(Finite Impulse Response, FIR)滤波器组对采样数据进行修正,可以在软件或硬件上实现。该方法的修正过程如图2所示,整个过程分为标定过程和修正过程两部分。

标定过程中,首先根据多个频点的采样结果进行失配误差标定,该过程通过正弦波四参数拟合方法实现,第m个通道的拟合结果可写为

其中:

$ {G}_{m} $ 、$ {\omega }_{m} $ 、$ {t}_{m} $ 、$ {o}_{m} $ 分别为其幅度、角频率、延时和直流分量。根据以上参数,即可计算得到各通道的失配误差,为了能够更加精确地描述失配误差随频率的变化,还需要插值计算得到足够多标定频点下的失配误差参数,且为配合后续计算,标定频点数应为2的幂次方。然后基于完美重构算法进行修正系数计算,在TIADC系统中,第m个通道含有失配误差的采样结果的频域表达式为其中:

$ {A}_{m}\left(j\omega \right) $ 为增益误差和相位误差的影响项;$ {B}_{m}\left(j\omega \right) $ 为偏置误差的影响项。而第m个通道理想采样结果的频域表达式$ {X}_{sm\_\mathrm{i}\mathrm{d}\mathrm{e}\mathrm{a}\mathrm{l}}\left(j\omega \right) $ 可根据采样原理得到,根据以上频域表达式可引入频域解为$ {F}_{m}\left(j\omega \right) $ 的修正滤波器,使得其满足完美重构方法组:即可达到消除失配误差影响的目的。通过求解以上方程组,即可得到第m个通道的修正滤波器的频域解

$ {F}_{m}\left(j\omega \right) $ ,由于修正过程是对时域波形进行FIR滤波,因此还需再通过快速傅里叶反变换(Inverse Fast Fourier Transform, IFFT)可将其转化为时域解$ {F}_{m}\left[n\right] $ ,此时时域解的阶数与标定频点数相同,在实时修正中如果直接用此时域解将会导致计算量过大,为了获得合适阶数的滤波器系数,还需要对时域解进行加窗截断,此时完成了修正系数的计算。利用标定过程求得的滤波器系数对失配误差进行修正,修正过程如图3所示。对于由M个采样通道组成的TIADC系统,输入信号

$ x\left(t\right) $ 由各个含有失配误差的通道进行采样,各通道采样结果为$ {x}_{sm}\left(t\right) $ 。$ {x}_{sm}\left(t\right) $ 经过量化与M倍上采样后得到$ {x}_{m}\left[n\right] $ ,然后利用完美重构滤波器对各个通道的采样序列分别进行滤波计算,最终将各个通道计算后的序列相加,即得到修正后的结果$ y\left[n\right] $ 。本工作所测试系统包含2个采样通道,故可对其进行2通道修正。

-

本节将详细介绍本系统测试的测试内容及各项测试内容的测试方法,并根据测试内容及方法介绍测试平台的搭建。

-

为验证系统能否正确采样以及修正方法是否有效,本系统的主要测试内容包括:模拟带宽测试、瞬态波形测试、失配误差测试和动态性能测试。

根据电气与电子工程师协会(Institute of Electrical and Electronics Engineers, IEEE) ADC测试标准[15],在ADC测试中,常常使用正弦波作为输入信号,主要原因是精确的正弦波源容易获得,并且基于频谱分析易于对采样结果进行分析。另外,正弦波作为线性时不变(Linear Time-Invariant, LTI)系统的特征函数,当单一频率的正弦波作为LTI系统的输入时,输出为仅幅度、相位改变的同频率正弦波,因此采样结果可反映非线性及时变误差。下面将详细介绍各项测试内容及对应的测试方法。

-

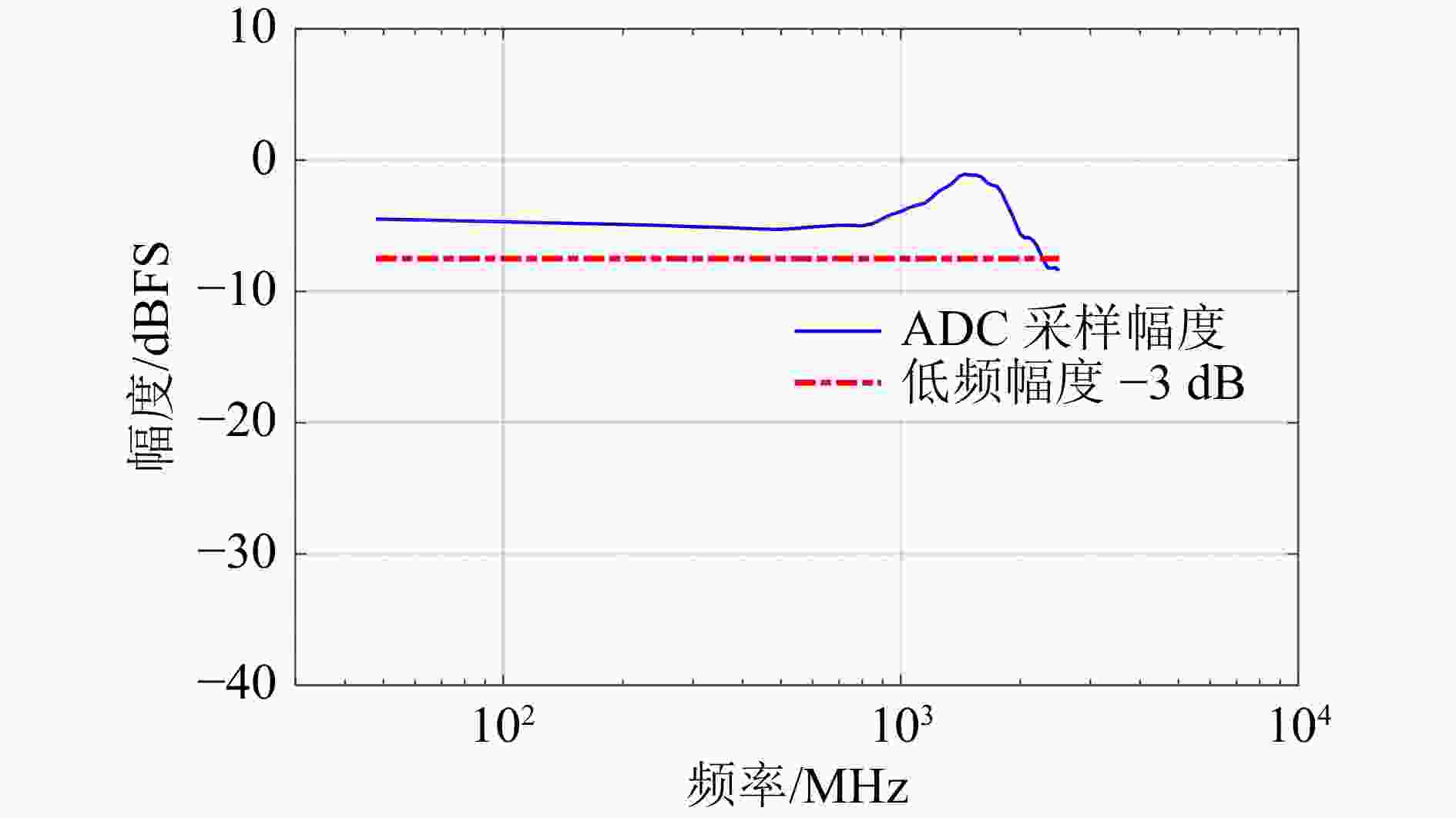

ADC采样结果的幅度往往会随着输入信号的频率变化而变化,ADC的模拟带宽(Bandwidth)是其频率响应的通带的频率宽度,具体定义为ADC增益与通带内某一特定参考频率处增益相差−3 dB的高频点与低频点的频率差,其中通带内参考频率应选在增益接近峰值处。对于绝大多数ADC,其通带范围向低频延伸至DC,此情况下,常常选取DC处的增益作为参考,将增益与DC处增益相差−3 dB的频率点定义为ADC的带宽。当输入信号的频率超出模拟带宽时,采样结果的幅度会有明显衰减,故模拟带宽反映了一个ADC采样系统能够测量的信号频率范围。为实现DC~1.25 GHz内的失配误差修正,本系统带宽应高于1.25 GHz。

带宽的测试方法是:使用单一频率的正弦波信号作为输入,固定输入信号的幅度,只改变信号的频率,对输入信号的频率进行扫描,通过正弦波拟合得到拟合结果

${y}_{\mathrm{f}\mathrm{i}\mathrm{t}} = A\mathrm{c}\mathrm{o}\mathrm{s}\left(2{\text{π} }ft+\varphi \right)+oht)+o$ ,其中$ A\mathrm{、}f $ 、$\varphi$ 、$ o $ 分别为采样得到的正弦波的幅度、频率、相位与DC偏置。根据各频点下系统采样后的信号幅度可得到系统采样结果的幅度随频率变化的曲线,即幅频响应曲线,找到采样幅度相对于低频下降3 dB的频点,此频率即为系统模拟带宽。测试中,输入信号应该具有高频谱纯度与低于被测试ADC的谐波失真,并且信号源在测试期间应具有稳定输出,且信号频率不能为ADC采样率的次谐波。根据Nyquist-Shannon采样定理[16],5 Gsps的采样系统能够正确采样的频率上限为2.5 GHz,故本系统带宽测试输入信号频率上限为2.5 GHz。

-

为保证系统能够实现5 Gsps的等效采样率,需要对其采样得到的瞬态波形进行测试与观察。

首先可以对单一频率正弦波采样结果进行测试,设定信号频率,调节信号源输出功率使得采样后正弦波拟合结果的幅度为−1 dBFS(dB relative to Full Scale),按照采样时钟将采样点顺序排列,即可观察系统采样得到的正弦波瞬态波形。

物理实验中,探测器输出信号多为脉冲信号,脉冲信号中含有丰富的频率成分,因此除正弦波外,还需要对脉冲信号进行测试。控制信号源发送脉冲信号,观察系统采样结果的波形,还可以将其与示波器直接采样得到的波形进行对比。

-

根据完美重构算法,为了进行失配误差修正,首先需要提取失配误差。根据1.2中给出的失配误差的定义,可以确定本系统失配误差测试的测试方法:

增益误差与相位误差随输入信号频率改变而改变,以单一频率正弦波作为输入信号,对频率进行扫描可得到上述两种失配误差随频率的变化趋势。单个频点增益误差与相位误差的测试方法为:设置信号源输出频率,调节信号源输出幅度,使得采样后正弦波拟合结果的幅度为−1 dBFS。对2片ADC各自的采样结果分别进行正弦波拟合,得到拟合结果

${y}_{\mathrm{fit}\_\mathrm{1,\, 2}} = {A}_{\mathrm{1,\,2}}\mathrm{cos}\left(2\text{π}ft+{\varphi }_{\mathrm{1,\,2}}\right)+{o}^{}_{\mathrm{1,\,2}}$ 。得到各个参数后,此频率下增益误差和相位误差可分别计算为:${G}_{2} = {A}_{2}/{A}_{1}$ ,${\Delta t}_{2} = \frac{{\varphi }_{2}-{\varphi }_{1}}{2\mathrm{\text{π} }f\left(\frac{{T}_{\mathrm{s}}}{2}\right)}$ ,其中$ {T}_{\mathrm{s}} $ 为单个ADC的采样周期,对应此系统中的400 ps。对于理想TIADC系统,${G}_{2} = 1$ ,${\Delta t}_{2} = 1$ 。改变信号源输出信号频率,调节输出幅度使得采样幅度保持−1 dBFS,在每个频点下进行上述拟合及计算过程,即可得到增益误差与相位误差随频率变化的趋势。偏置误差一般只与采样率有关,可视为一与信号频率无关的恒定值,单一频点的偏置误差为:

${\Delta o}^{}_{2} = {o}^{}_{2}-{o}^{}_{1}$ ,通过计算各个频点的偏置误差,再对所有频点的偏置误差求平均即可得到。 -

一个ADC系统的性能参数主要分为静态参数[16]与动态参数[17],静态参数主要包括微分非线性与积分非线性,这两种非线性描述了ADC的实际码值与理想码值的偏差,静态参数一般由ADC自身决定,而动态性能不仅与ADC有关,还与电源纹波、输入信号、外部电路有关,并且失配误差主要影响系统的动态性能,因此动态性能是本TIADC系统的测试重点。动态性能主要有:信噪比(Signal-to-Noise Ratio, SNR)、总谐波失真(Total Harmonic Distortion, THD)、信纳比(Signal-to-Noise-And-Distortion ratio, SINAD)、无伪峰动态范围(Spurious Free Dynamic Range, SFDR)和有效位(Effective Number of Bits, ENOB)。

1) 信噪比(SNR)

ADC的SNR为在规定振幅和频率的单一频率正弦波输入下ADC采样结果的频谱中信号成分的能量

$ {P}_{\mathrm{s}\mathrm{i}\mathrm{g}\mathrm{n}\mathrm{a}\mathrm{l}} $ 与去除直流成分与谐波成分后的噪声成分的能量$ {P}_{\mathrm{n}\mathrm{o}\mathrm{i}\mathrm{s}\mathrm{e}} $ 之比,计算公式为其中噪声的来源有量化噪声、采样时钟噪声、ADC本身的噪声以及ADC外围电路的噪声等。

2) 总谐波失真(THD)

采样过程中,ADC的非线性不可避免,采样结果的频谱中必然存在谐波,ADC的THD为在规定振幅和频率的单一频率正弦波输入下ADC采样结果的频谱中谐波成分的总能量

$ \sum {P}_{\mathrm{h}\mathrm{a}\mathrm{r}\mathrm{m}\mathrm{o}\mathrm{n}\mathrm{i}\mathrm{c}} $ 与信号能量之比,计算公式为由于谐波有无穷多个,计算谐波总能量时无法将所有谐波能量统计在内,一般只计算2~10次谐波能量即可。

3) 信纳比(SINAD)

ADC的SINAD为在规定振幅和频率的单一频率正弦波输入下采样结果频谱中信号成分能量与噪声能量和谐波总能量和的比值,计算公式为

由于SINAD考虑了噪声与谐波,相比SNR,SINAD更能真实地反映ADC的性能。

4) 无伪峰动态范围(SFDR)

ADC的SFDR为在规定振幅和频率的单一频率正弦波输入下采样结果频谱中信号成分能量与整个Nyquist区内观察到的最大非信号峰(伪峰)能量

$ {P}_{\mathrm{s}\mathrm{p}\mathrm{u}\mathrm{r}\mathrm{s}\_\mathrm{h}} $ 的比值,计算公式为5) 有效位(ENOB)

由于噪声、非线性等非理想因素存在,ADC的采样结果中可置信的位数往往不能达到设计的分辨位数,ENOB表示ADC输出结果中实际可置信的位数,其经验公式为

为了对系统修正前后的性能进行对比,需对此系统进行动态性能测试,以验证修正过程有效性。各项动态性能均为输入信号频率的函数,动态性能的测试同样使用单一频率正弦波作为输入信号,对采样结果进行频谱分析获得动态性能参数。由于失配误差修正过程中无法对ADC的非线性进行修正,因此本系统测试中不需关注THD,只需要关注与失配误差有关的SNR、SINAD、SFDR及ENOB。

测试某一特定频点的动态性能时,调节信号源输出指定频率的单一频率正弦波,调节信号源输出幅度使得ADC采样结果的幅度为−1 dBFS,得到系统对此输入信号的采样结果。快速傅里叶变换(Fast Fourier Transformation, FFT)是一种高速算法,能够快速实现有限长度的离散信号从时域到频域的转换,对采样结果进行FFT分析即可得到输出结果的频谱。在每次采样中,由于随机白噪声的存在,FFT得到的频谱的噪声平台涨落较大,不便于分析,针对此问题,可以采用多次FFT谱平均的方法降低噪声平台的涨落,从而使得各个信号峰更加清晰地呈现于频谱中。

在进行FFT分析时,采样点数应为2的幂次方,这意味着需要对无限长的采样序列进行截断,截断操作可能会导致频谱泄露现象。如果在测试过程中能够严格满足相干采样条件,即可避免FFT分析时的频谱泄露。但在实际的ADC测试中,严格满足相干采样条件是很难做到的,在对采样序列进行FFT分析前,对采样序列加窗函数处理可以有效减轻频谱泄露。

利用FFT分析得到的频谱,可评估SNR、SINAD、SFDR、ENOB等动态性能。对

$ N = {2}^{n} $ 个点进行FFT计算得到的频谱是一个离散函数,在DC到$ {f}_{\mathrm{s}}/2 $ 的第一Nyquist区中共有$({2}^{n-1}+1)$ 个点,每个点对应一个频率值$ f $ ,第m个点对应的频率值为${f}_{m} = \frac{m-1}{N}\times {f}_{\mathrm{s}}$ ,对应的幅度为该点对应的信号能量,可记为$ P\left[f\right] $ 。频谱中的最高峰对应信号峰,根据其位置可以计算信号频率$ {f}_{\mathrm{s}\mathrm{i}\mathrm{g}\mathrm{n}\mathrm{a}\mathrm{l}} $ ,确定信号频率后,在其附近设定一定范围,即设定统计能量的开窗大小$ \mathrm{w}\mathrm{i}\mathrm{n} $ ,计算该范围内频谱的总能量,即为信号的能量$ {P}_{\mathrm{s}\mathrm{i}\mathrm{g}\mathrm{n}\mathrm{a}\mathrm{l}} $ ,计算公式为确定信号频率后可推算谐波位置,如果谐波在Nyquist带宽区间内,其位置可直接得到;如果谐波在Nyquist带宽区间外,其位置可通过在Nyquist区间内镜像得到。用同样的方法可以计算谐波能量,第n次谐波能量可以表示为

总谐波能量

$ \sum {P}_{\mathrm{h}\mathrm{a}\mathrm{r}\mathrm{m}\mathrm{o}\mathrm{n}\mathrm{i}\mathrm{c}} $ 一般可由第2~10次谐波能量的和表示:除去信号能量与总谐波能量后,频谱上其余的能量值即为噪声能量

$ {P}_{\mathrm{n}\mathrm{o}\mathrm{i}\mathrm{s}\mathrm{e}} $ ,失配误差产生的伪峰能量也包含在其中,其计算公式为除此之外,在频谱中找到能量最高的非信号峰(最大伪峰),用同样的方法可计算最大伪峰能量

$ {P}_{\mathrm{s}\mathrm{p}\mathrm{u}\mathrm{r}\mathrm{s}\_\mathrm{h}} $ 。有了以上能量值,根据式(4)~(8),即可计算该频率下各个动态性能参数的值。对信号频率进行扫描,即可得到系统在频带范围内动态性能随频率的变化趋势。本系统数据分析过程中,每次FFT分析采样数据数为16 384个,这对于FFT分析得到的频谱已具有较高的频率分辨。谱平均次数为15次,15次谱平均后采样结果噪声平台的涨落较小,各个能量峰清晰呈现在频谱中。在对数据进行FFT分析之前加布莱克曼窗处理,它具有主瓣宽且幅值大、旁瓣宽度小、衰减速度快的特点,可有效抑制频谱泄露现象。

-

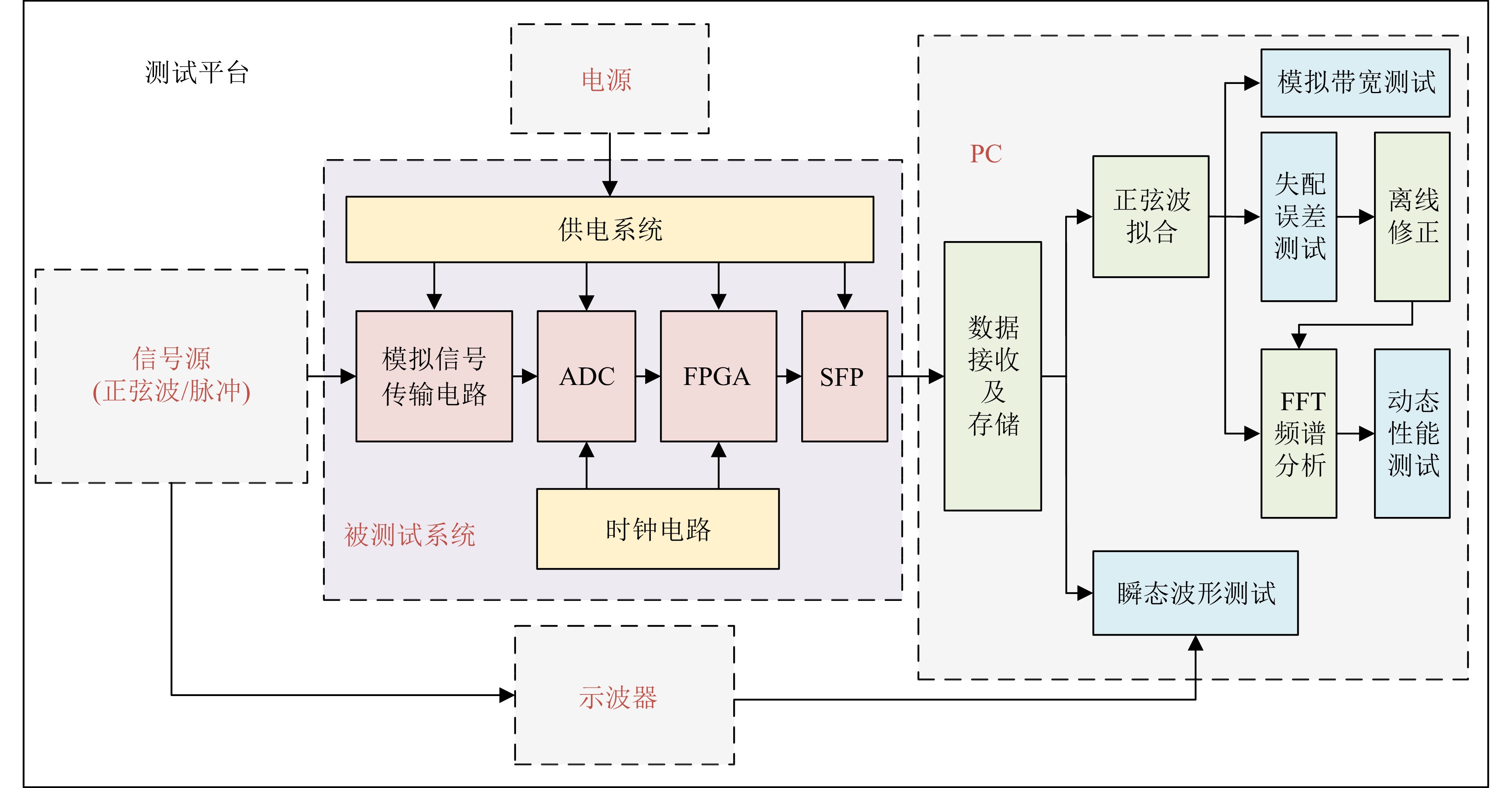

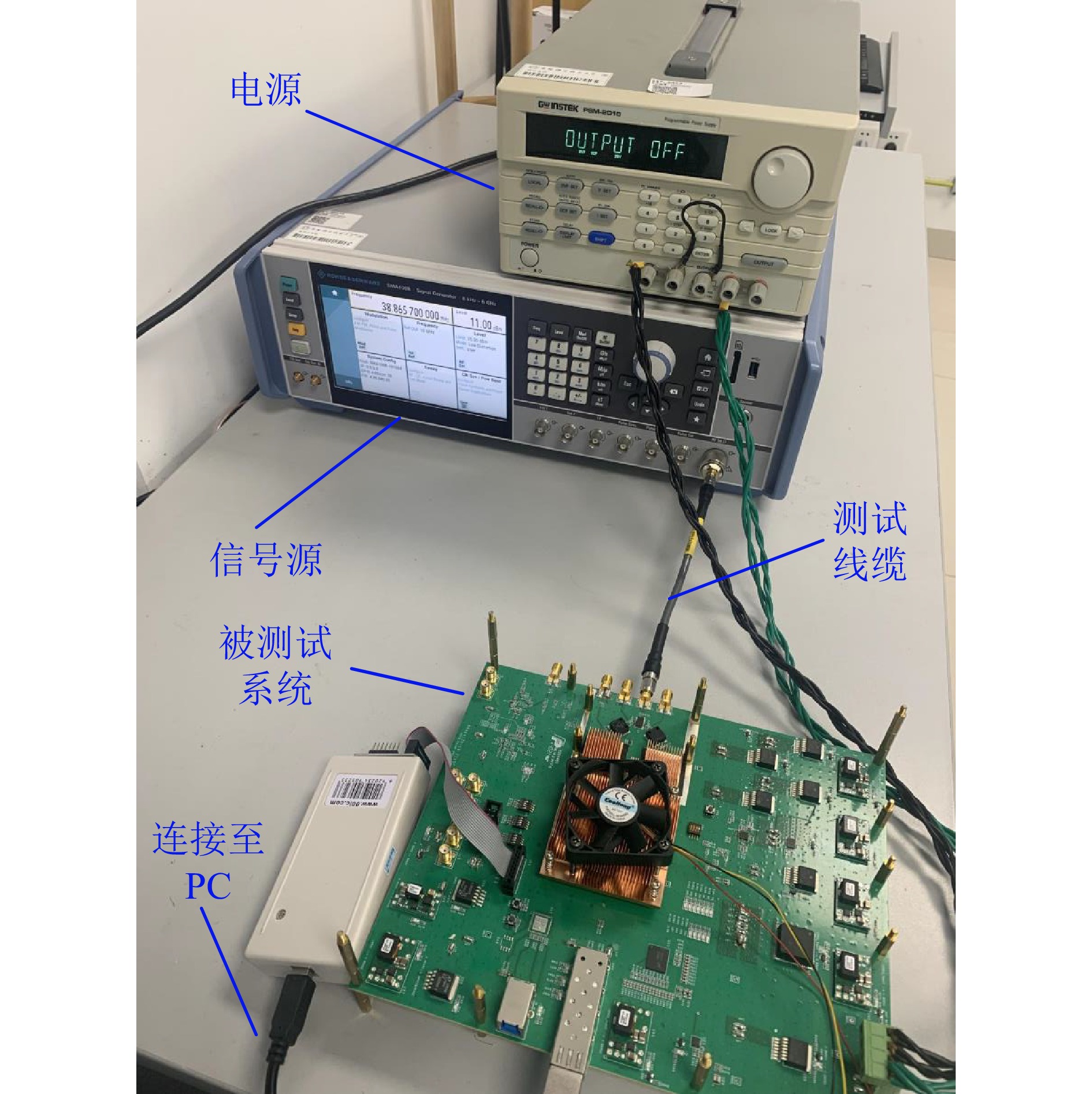

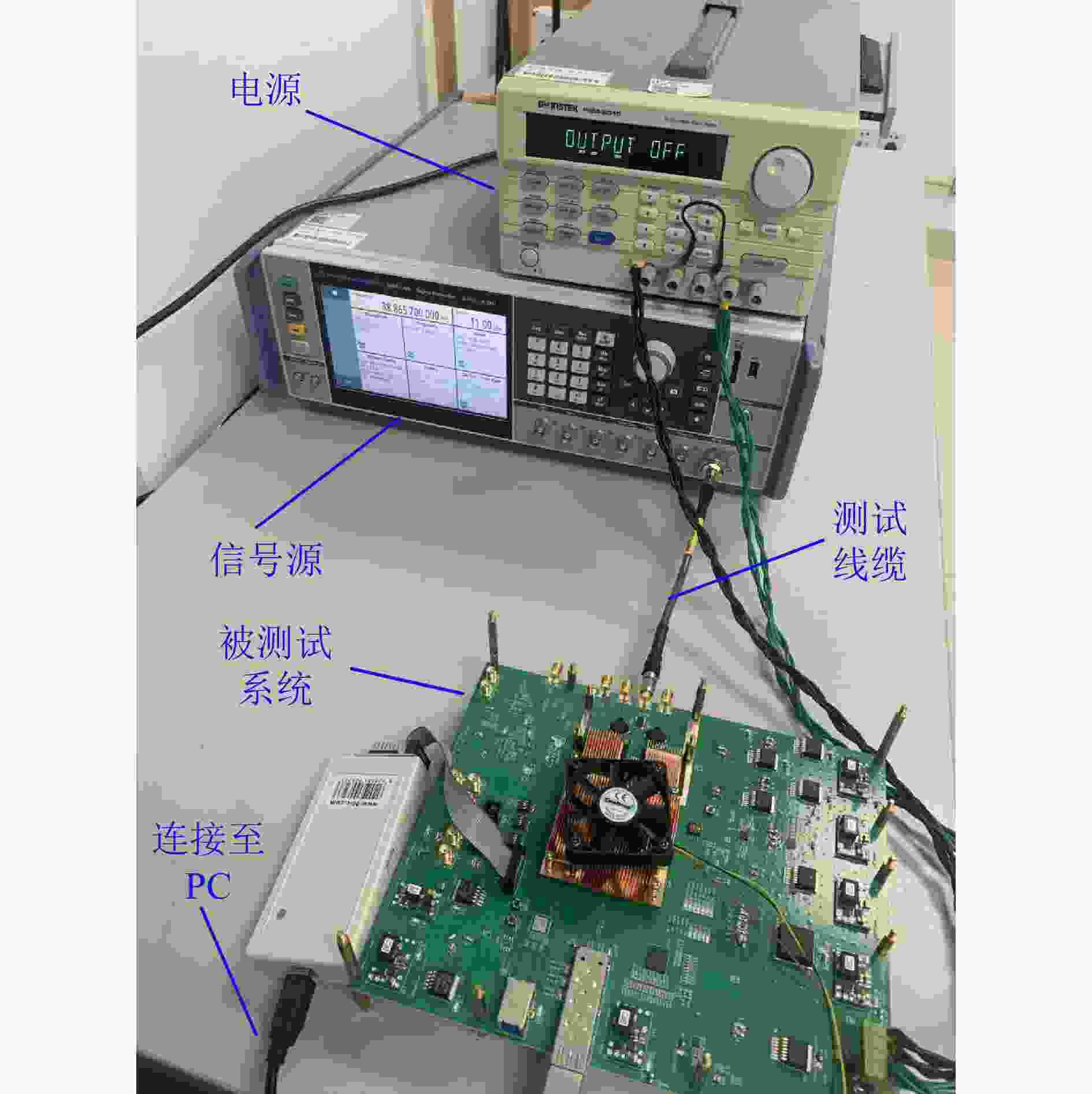

根据上述测试内容及方法,可搭建本系统的测试平台,测试平台结构如图4所示,其主要由信号源、电源、被测试系统、示波器与PC组成。信号源输出正弦波或脉冲信号,电源为被测试系统供电,被测试系统可对输入信号进行采样,示波器可直接对信号源输出信号进行采样,用以与系统采样波形的对比,PC对采样结果进行接收、存储,然后可在软件中对数据进行相应处理及分析。

各项测试中,均需使用单一频率的正弦波作为输入信号,正弦波信号频率覆盖DC~2.5 GHz,因此需要能够产生上述频率范围的射频信号源。在失配误差及动态性能测试中需控制采样幅度为−1 dBFS,另外ADC测试中对信号源输出品质和稳定性都有较高要求。综上考虑,本系统测试中选择了一款射频信号发生器,其型号为Rohde&Schwarz SMA100B-106。该信号源可提供高品质的稳定正弦波输出,输出信号幅度范围−145~20 dBm,频率范围8 kHz~6 GHz,相位噪声−135 dBc@1 GHz & 20 kHz offset和−155 dBc@1 GHz &>10 MHz offset。

在瞬态波形测试中还需要对脉冲信号进行采样,因此除正弦波信号源外,还需要脉冲信号源,信号源应可以产生上升/下降沿可配置的脉冲输出,并且输出幅度应可配置以适应ADC的输入信号幅度范围。本系统脉冲信号源选择了任意波形发生器Keysight 81160A,该信号源可配置产生最快上升/下降沿1 ns的脉冲波形,输出信号幅度范围为50 mVpp~5 Vpp。

在脉冲测试中,使用示波器对被测系统采样得到的波形与实际波形进行对比,测试中选取的示波器为Lecroy WavePro 254HD,该示波器有4个输入通道,分辨率12 bits,最高采样率20 Gsps,−3 dB模拟带宽2.5 GHz,输入可选50 Ω DC耦合或1 MΩ AC/DC耦合。

被测试TIADC系统供电系统采用12 V电压供电,经初步估计在系统工作时需要电流为几A,且电源噪声也会对系统性能有所影响。因此应该选择输出最高电压高于12 V且噪声较小的电源为TIADC系统供电。本系统选取了一款直流稳压电源,其型号为GWINSTEK PSM-2010,该电源有0~8 V/20 A与0~20 V/10 A两个输出档位可选择,电源输出噪声<350

$\mathrm{\mu }{\mathrm{V}}_{\mathrm{r}\mathrm{m}\mathrm{s}}$ 。使用0~20 V/10 A档位可为测试系统供电。除上述需要使用的仪器外,由于本系统测试中输入信号的频率高达GHz量级,普通的传输电缆在进行高频信号传输时衰减较大,故需要使用低插入损耗的测试电缆。本系统测试中选用了一根长度为20 cm的高带宽低衰减同轴电缆进行模拟输入信号的传输。

使用上述仪器及电缆即可搭建本系统的测试平台,测试平台照片如图5所示。

-

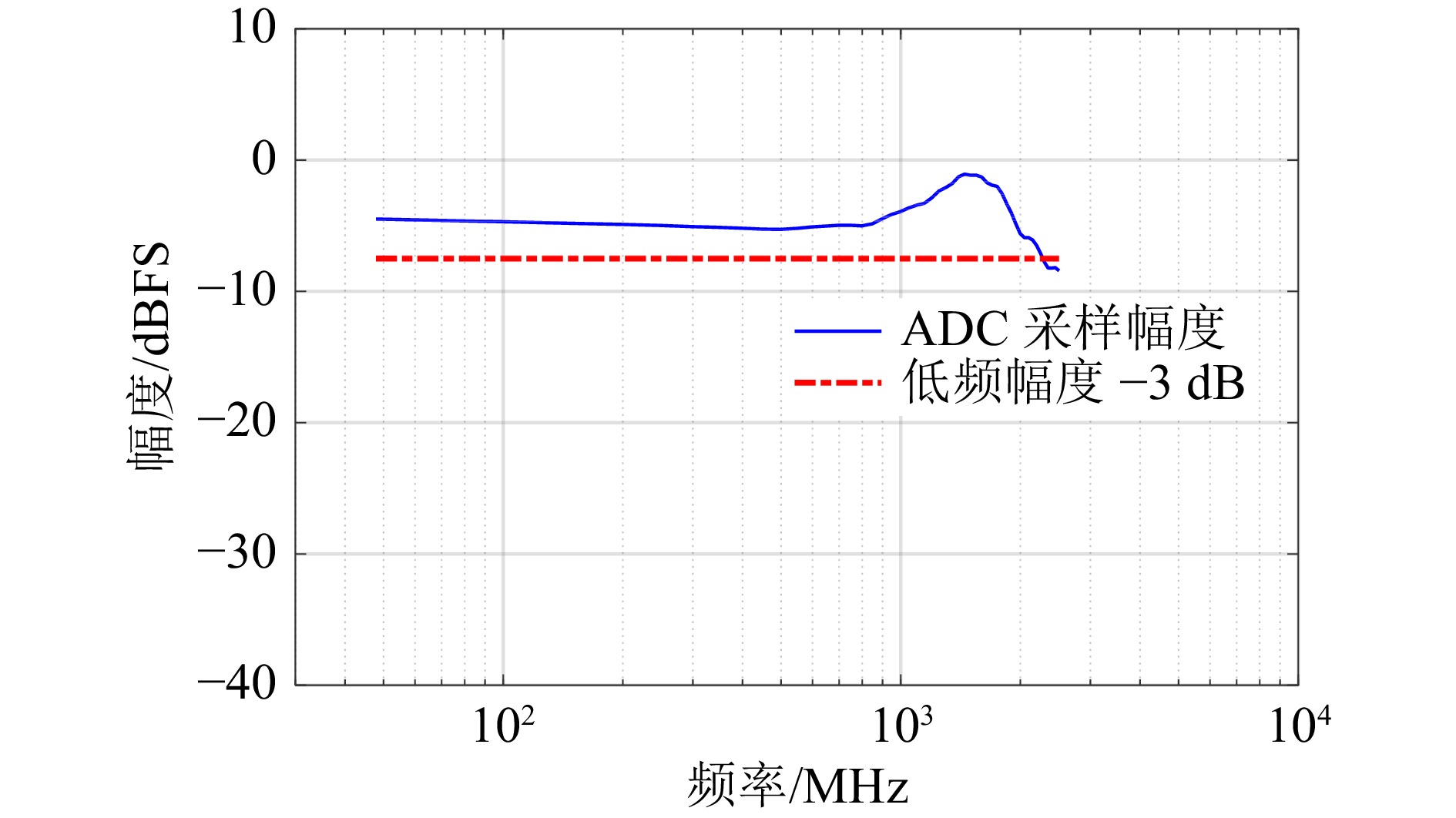

本系统带宽测试结果如图6所示,本系统带宽达2.2 GHz,超过了1.25 GHz的修正频率上限。

-

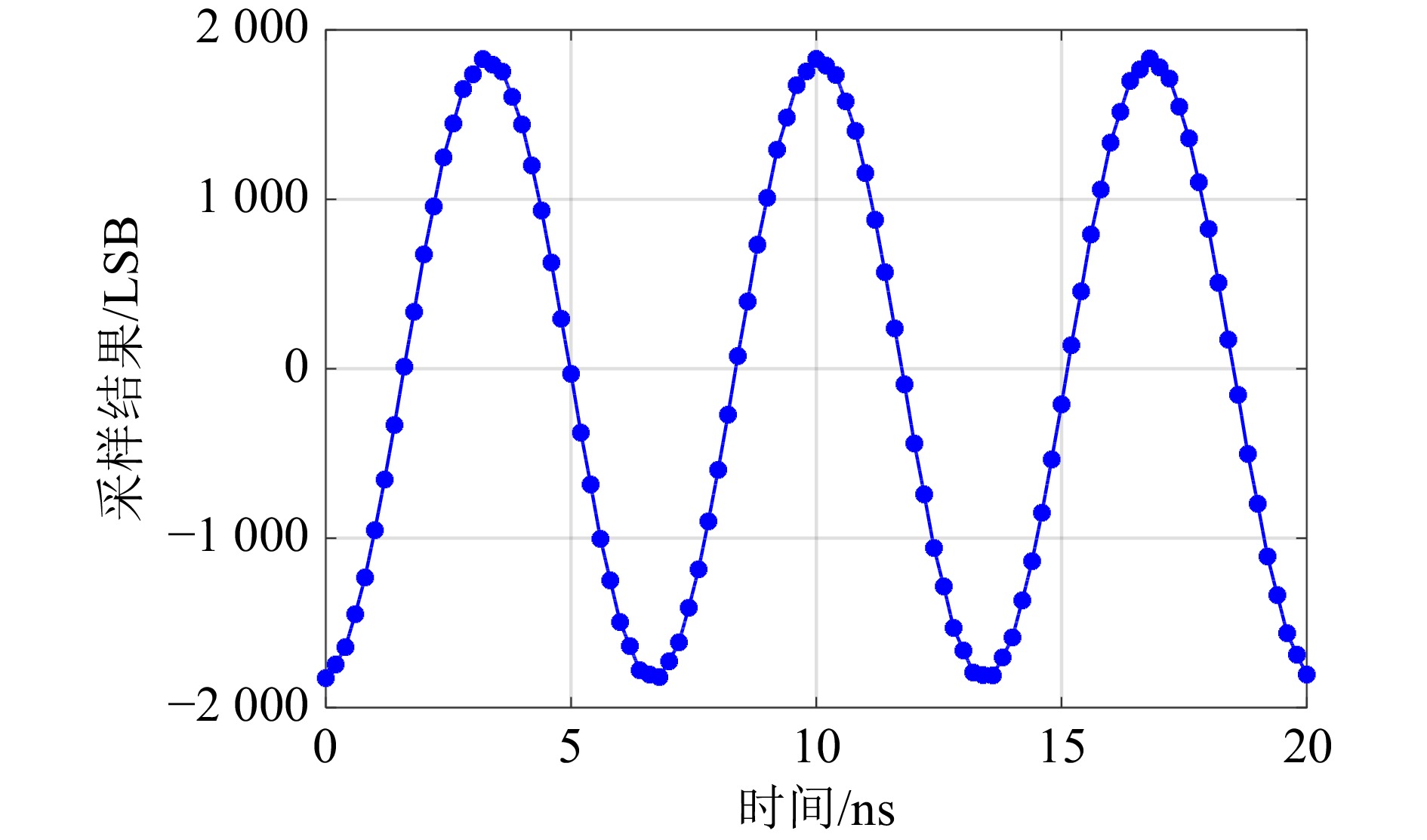

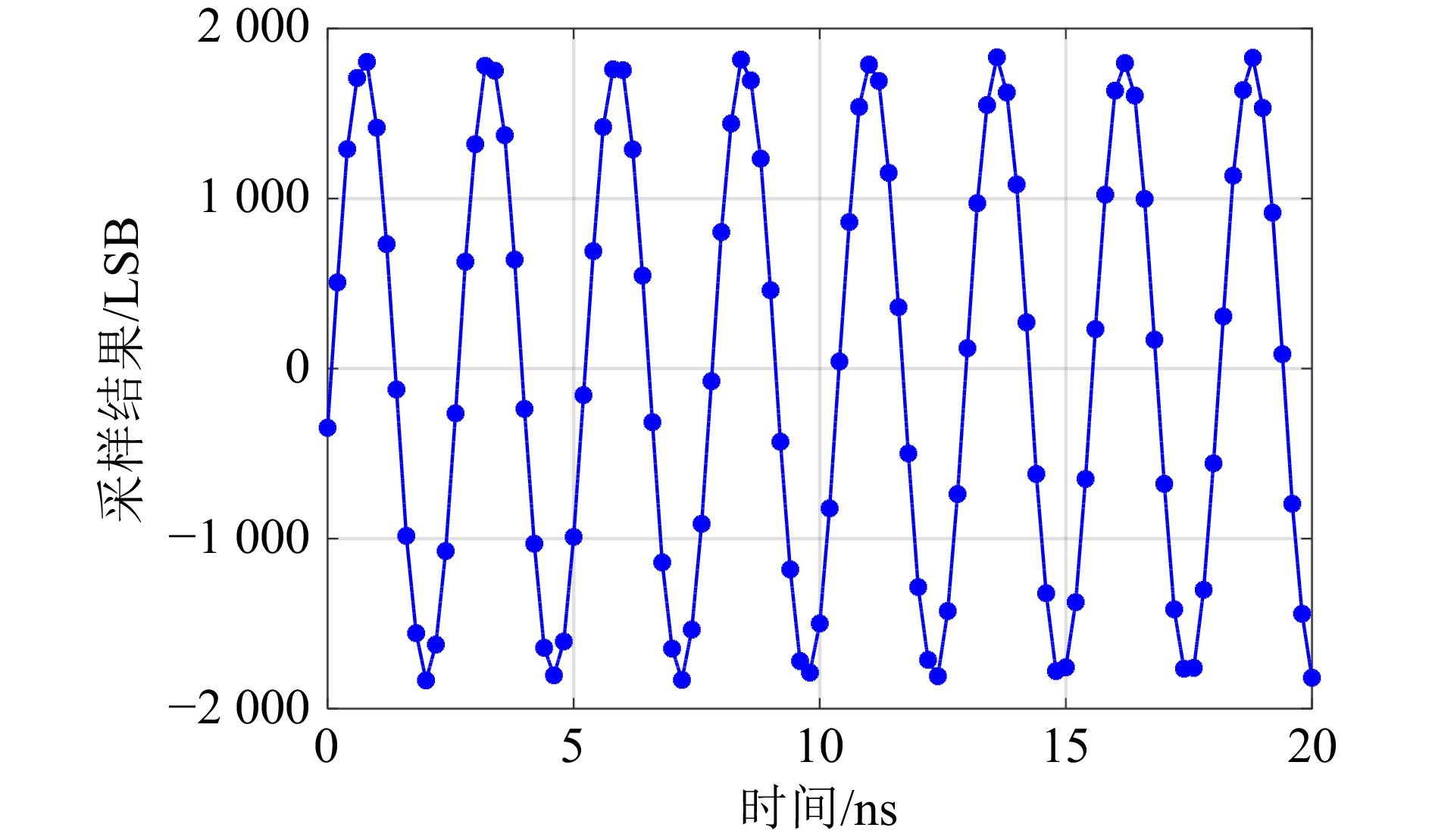

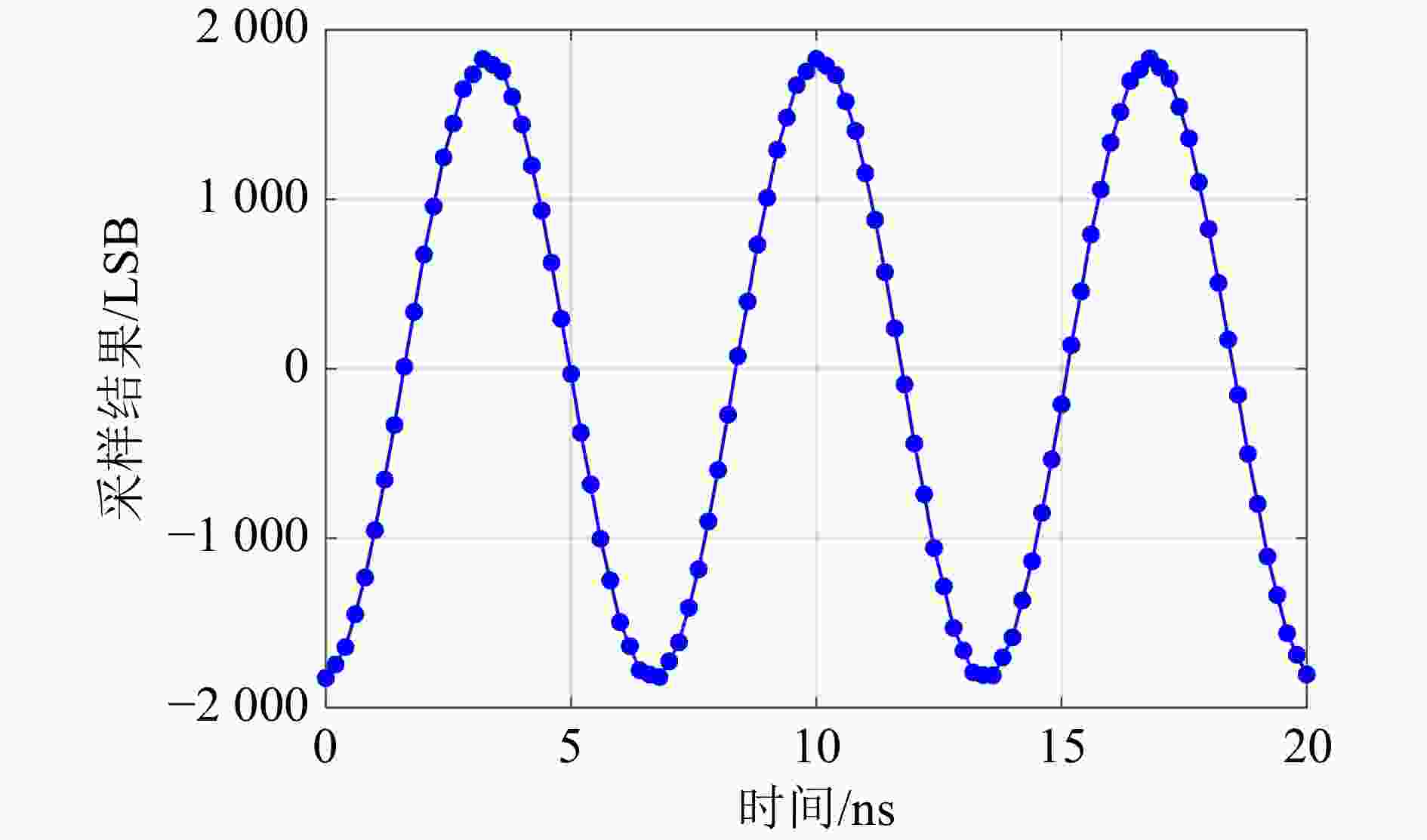

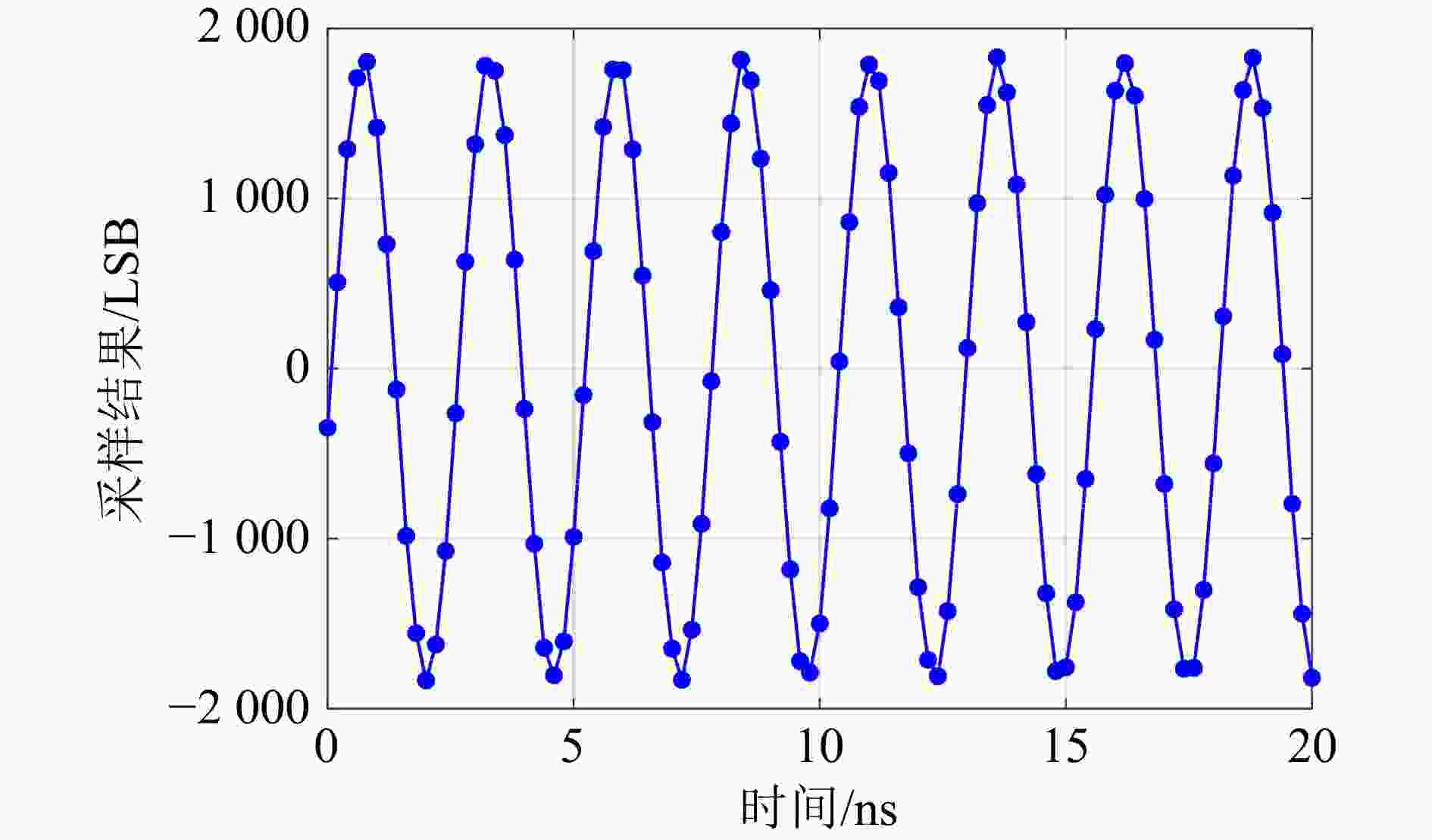

对系统进行瞬态波形测试,首先是单一频率正弦波测试。输入147和387 MHz正弦波时系统采样得到的瞬态波形如图7和图8所示。

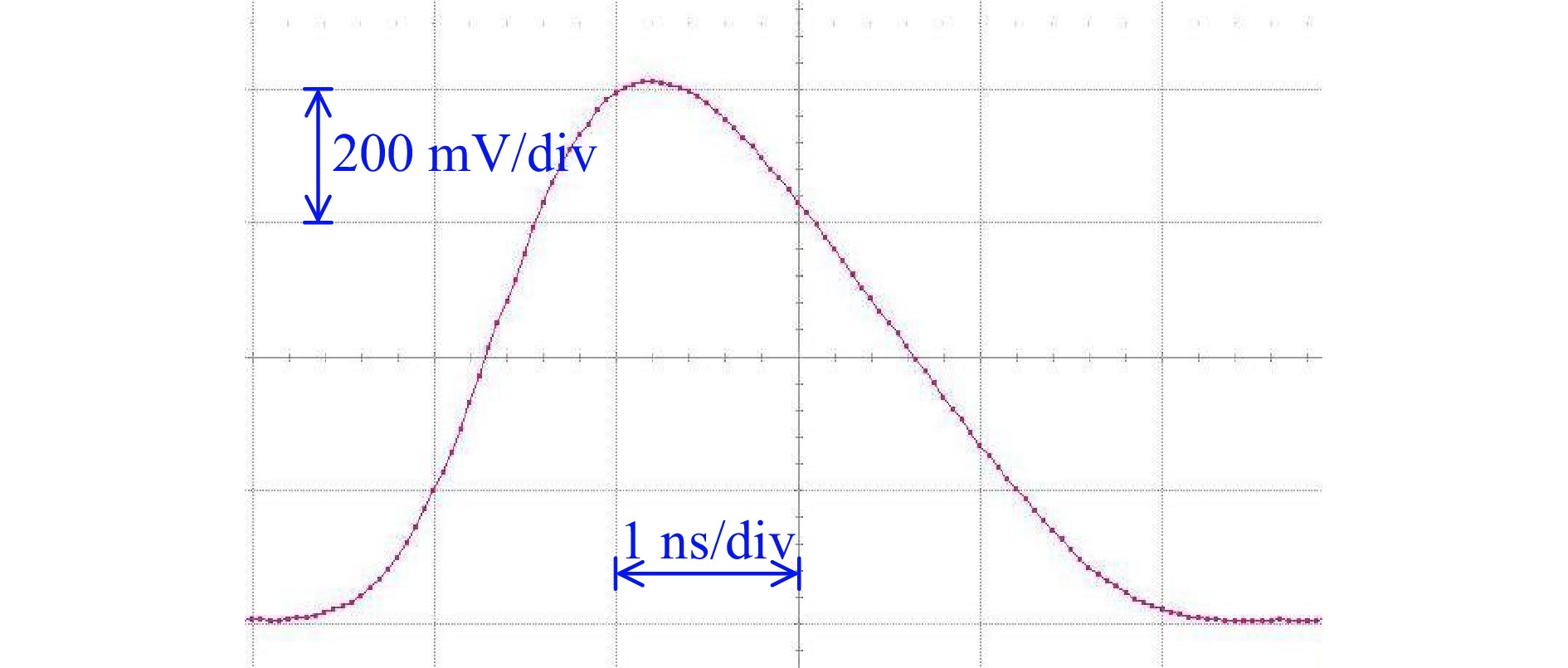

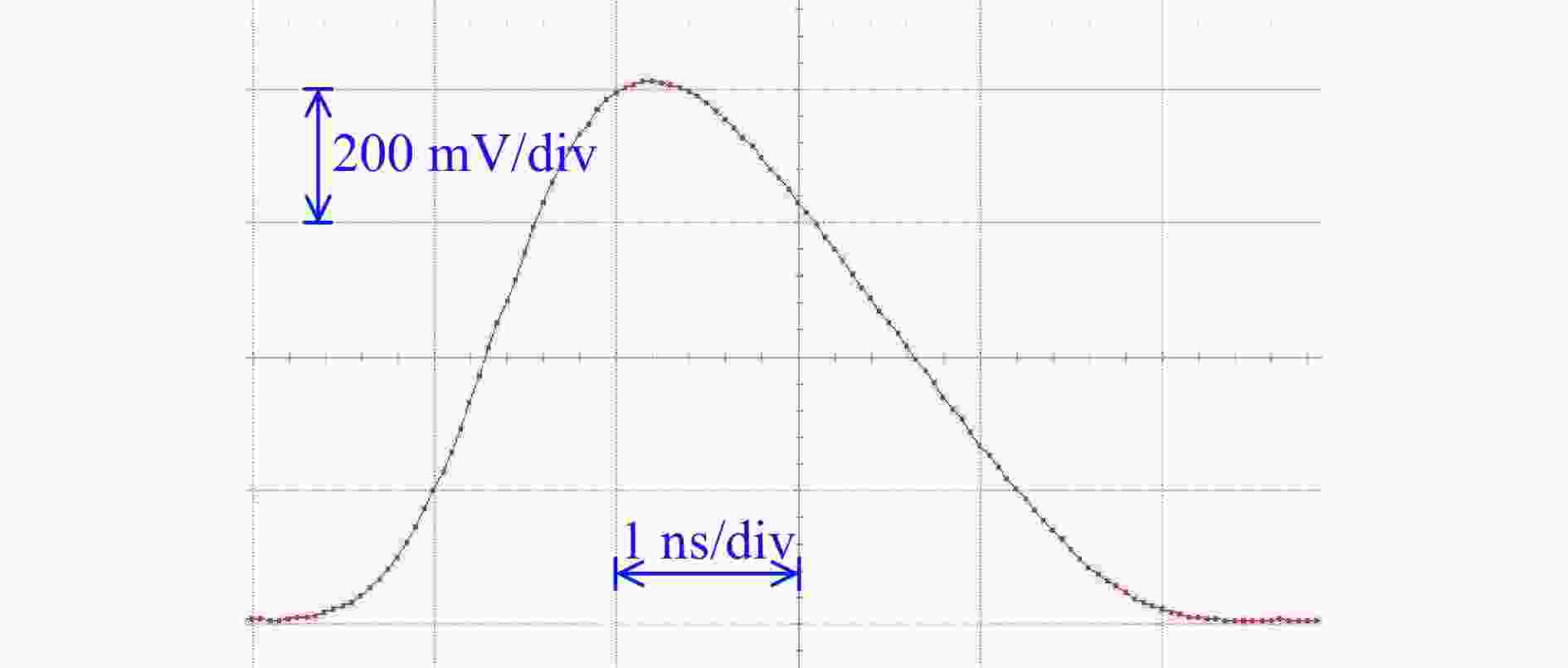

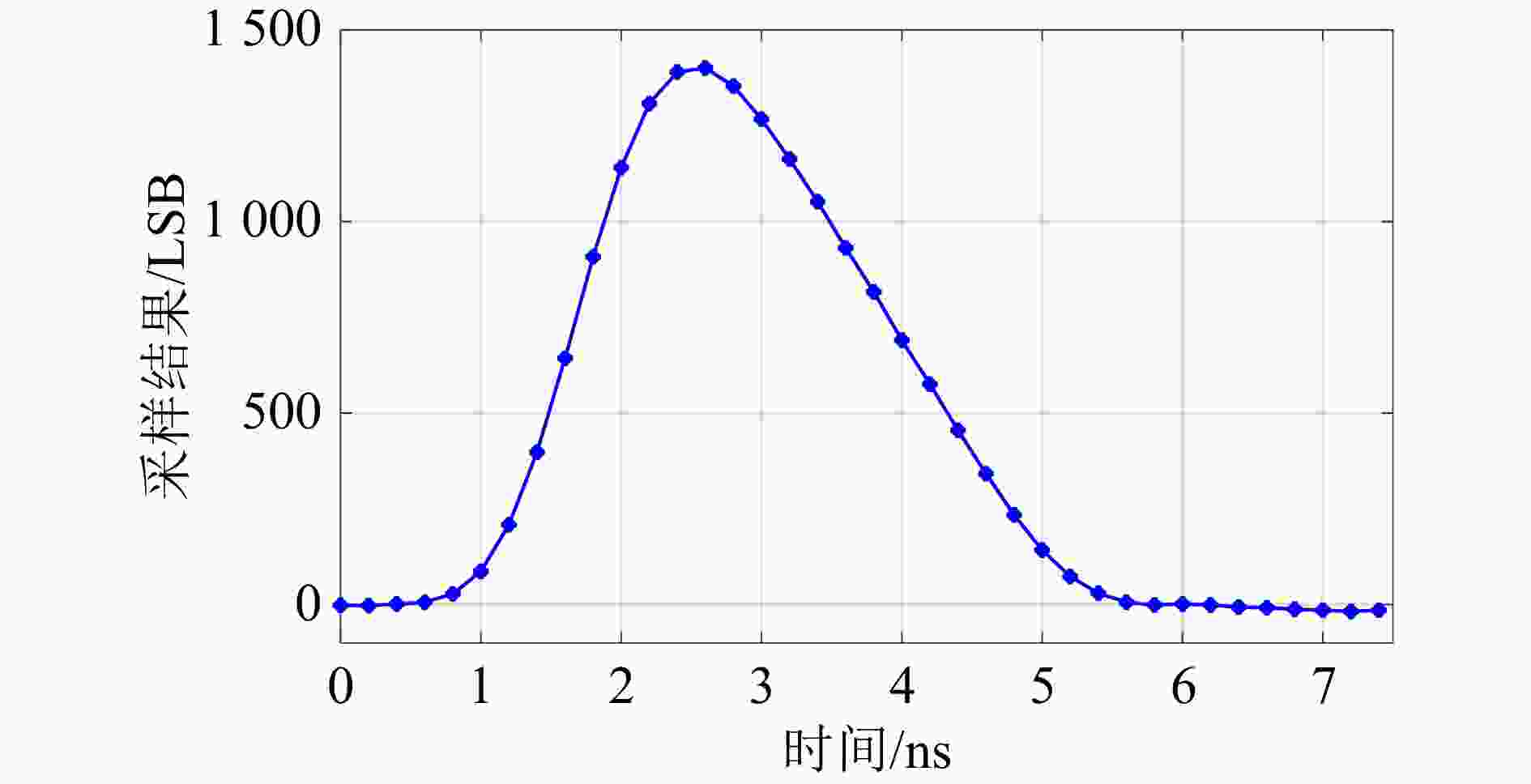

然后是脉冲波形测试,由信号源产生一个上升沿1 ns,下降沿2 ns的脉冲,示波器采样得到的波形如图9所示。本系统对信号采样得到的波形如图10所示。

上述结果表明本系统可以200 ps的时间间隔对输入信号正确采样,即利用2片采样率为2.5 Gsps的ADC实现了5 Gsps的等效采样率。

-

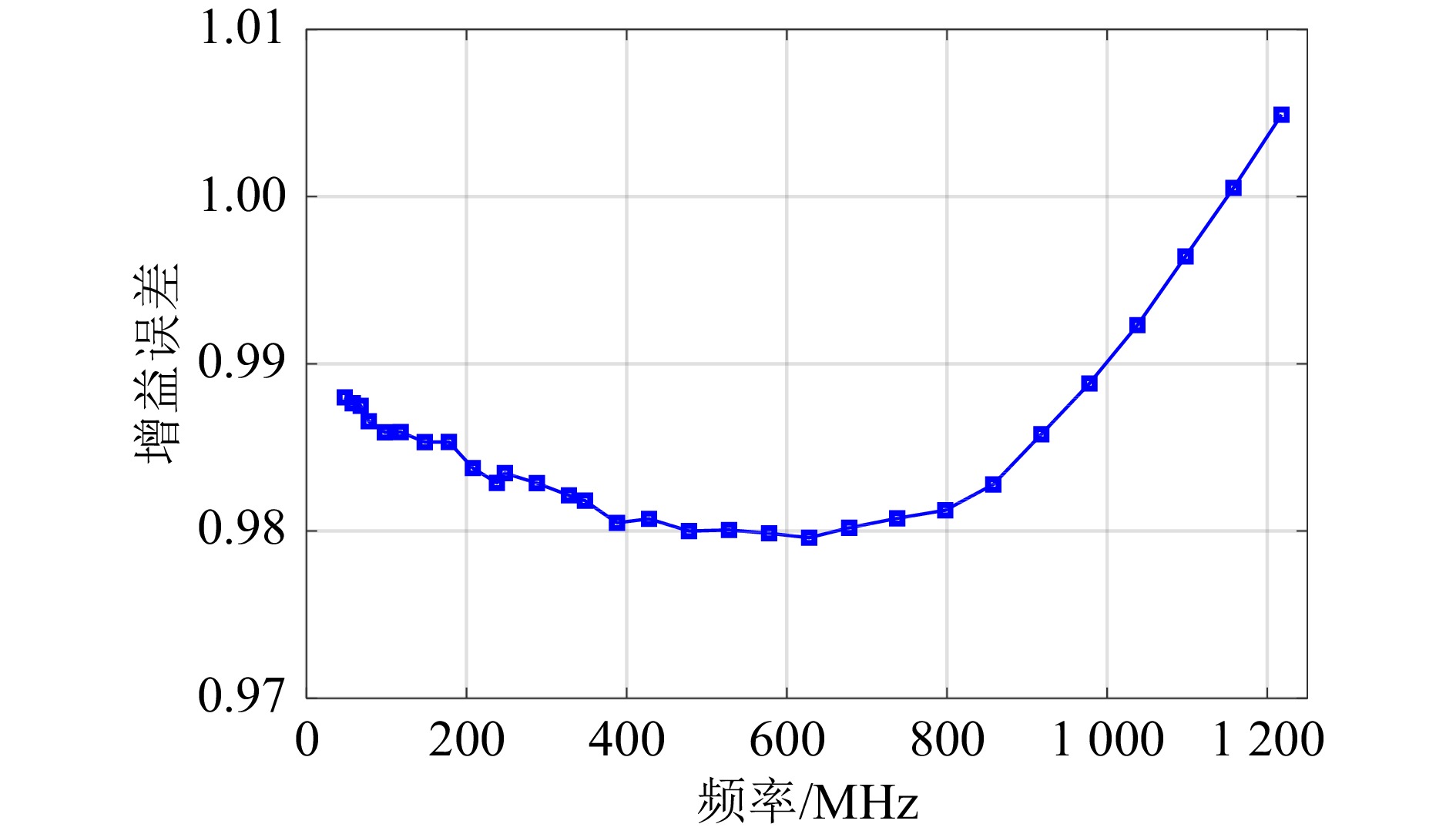

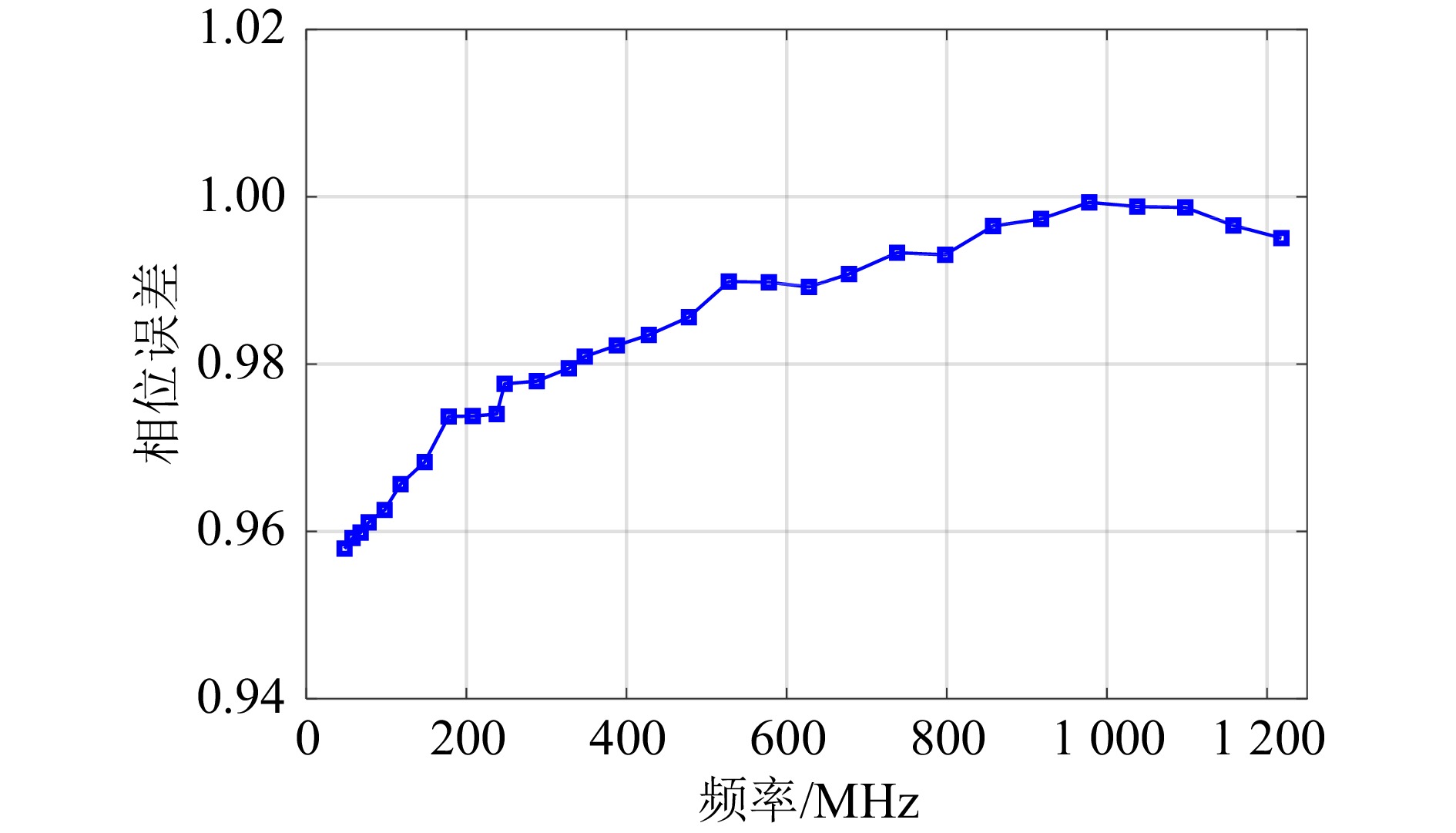

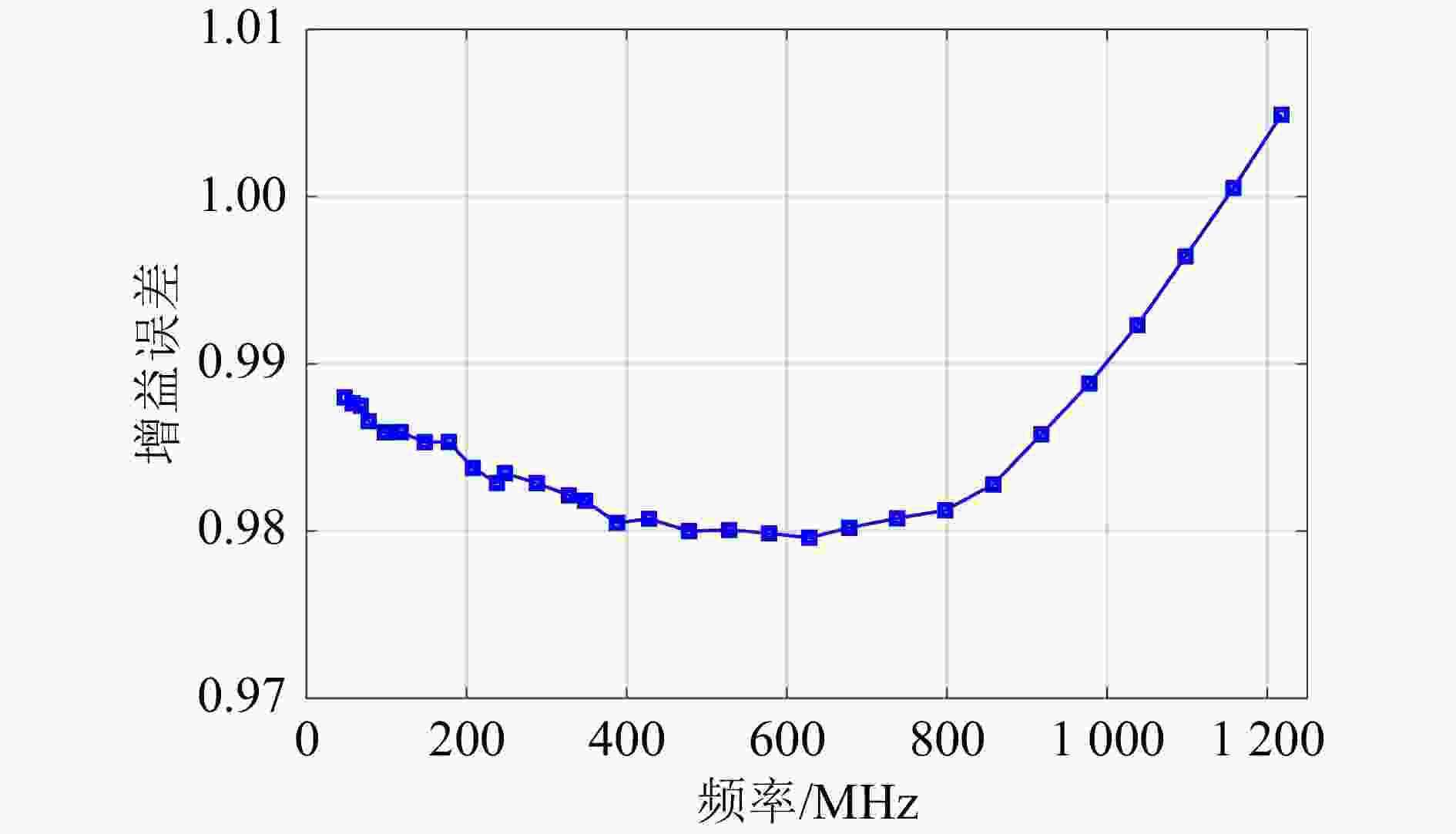

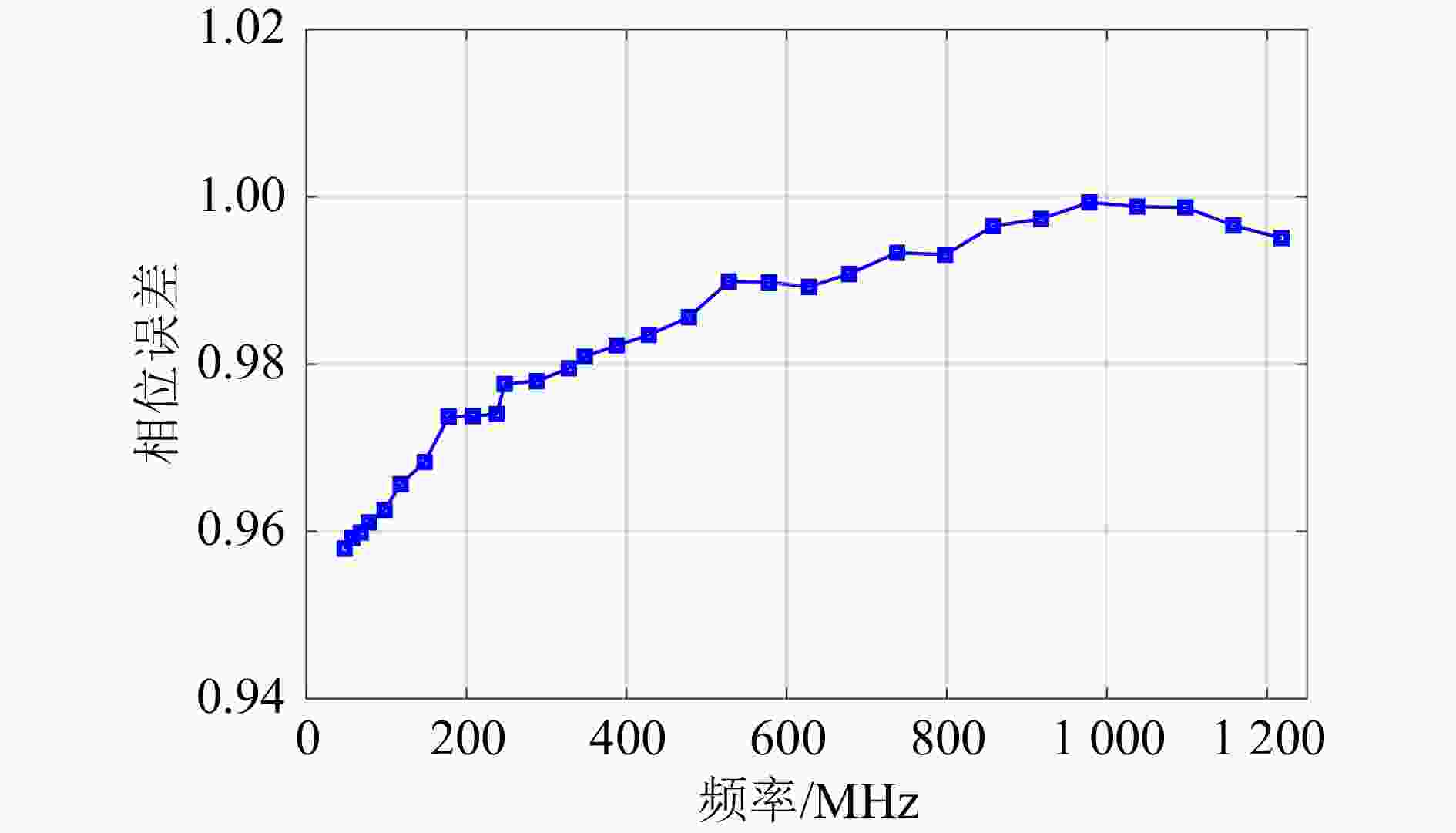

本系统增益误差和相位误差测试结果如图11和图12所示,在DC~1.25 GHz范围内,增益误差变化范围为0.980~1.005,相对于理想值1浮动范围为2.5%。相位误差变化范围为0.958~0.999,相对于理想值1浮动范围为4.1%,对应的采样时间误差为0.2~8.4 ps。

-

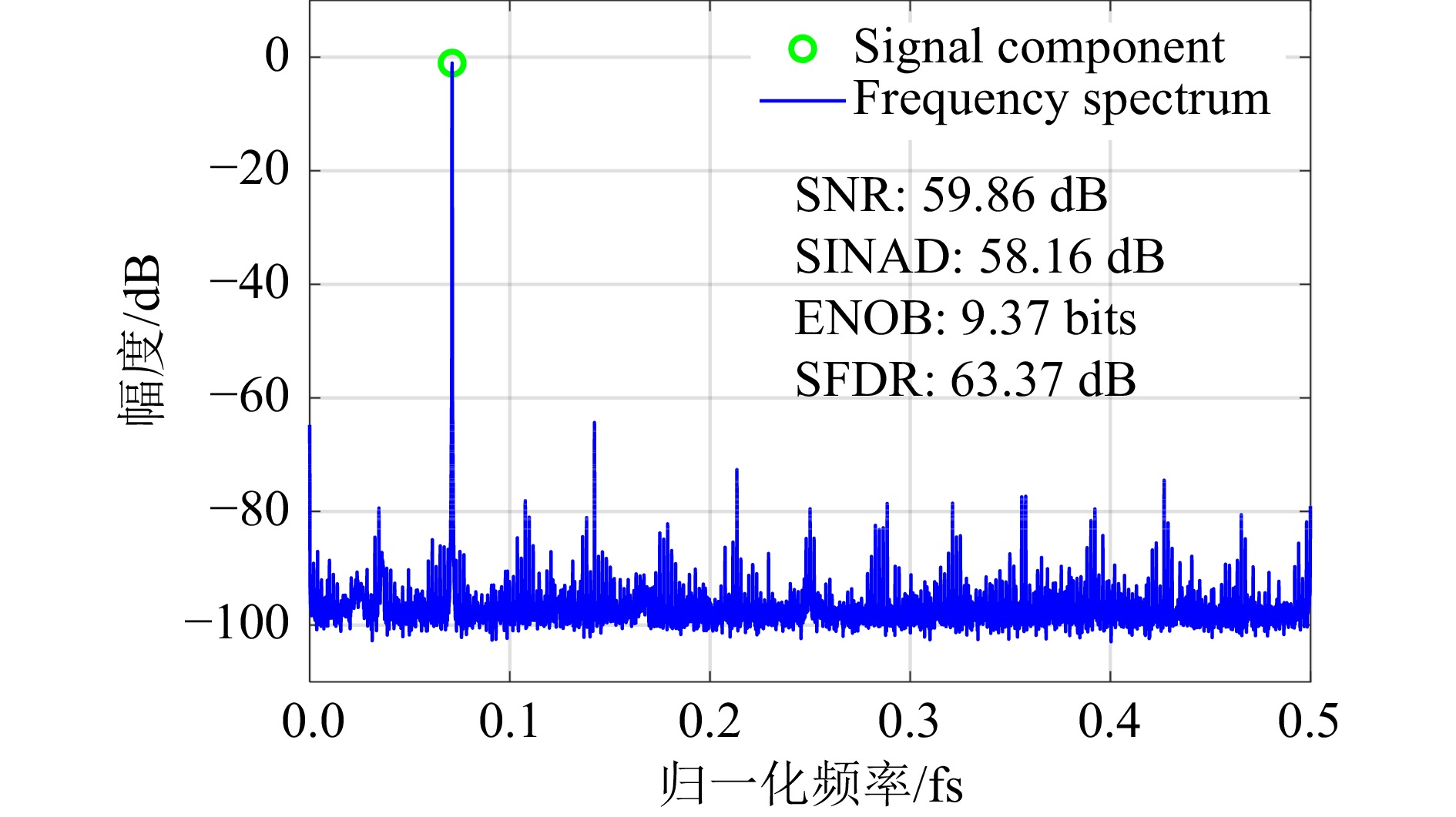

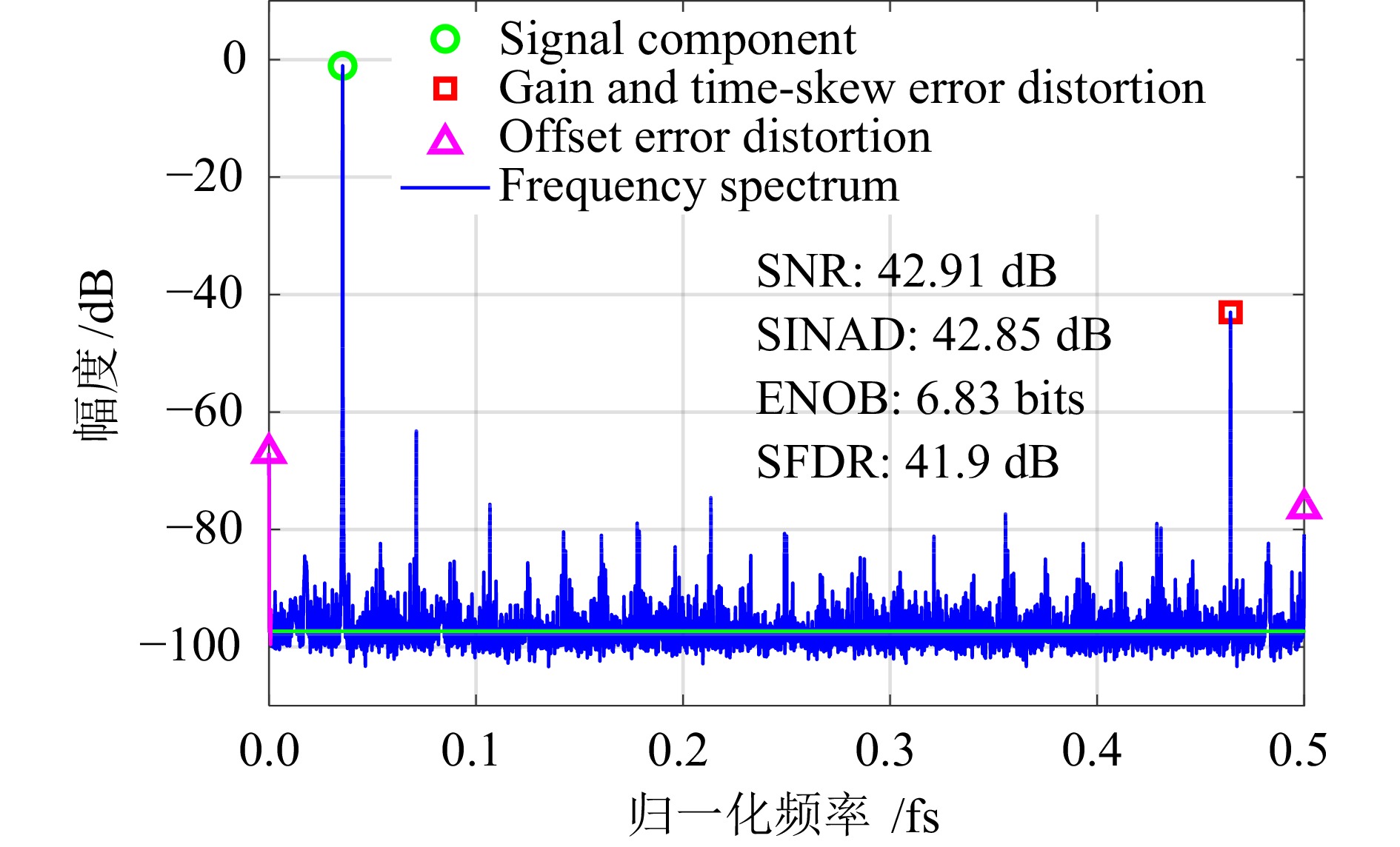

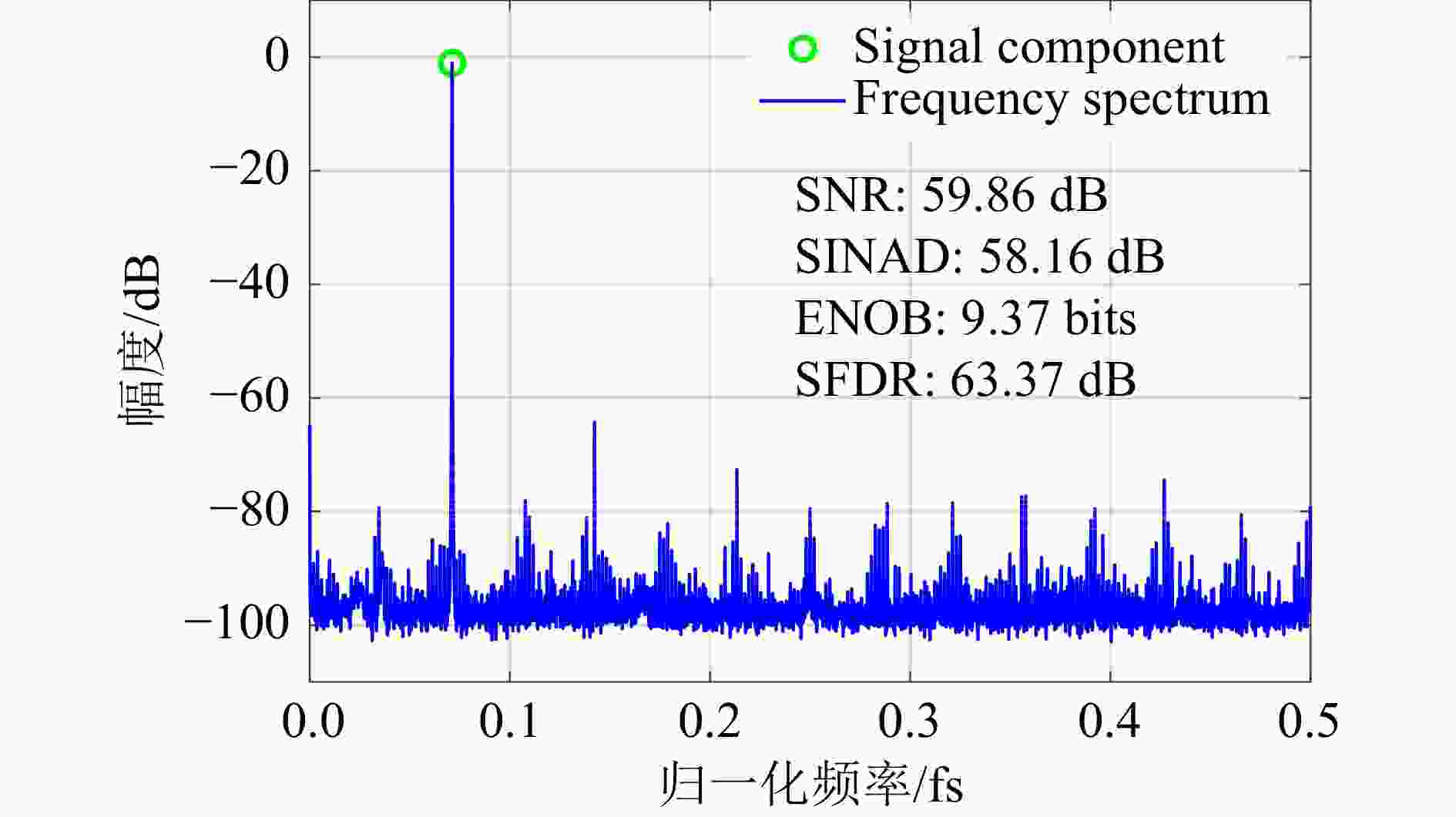

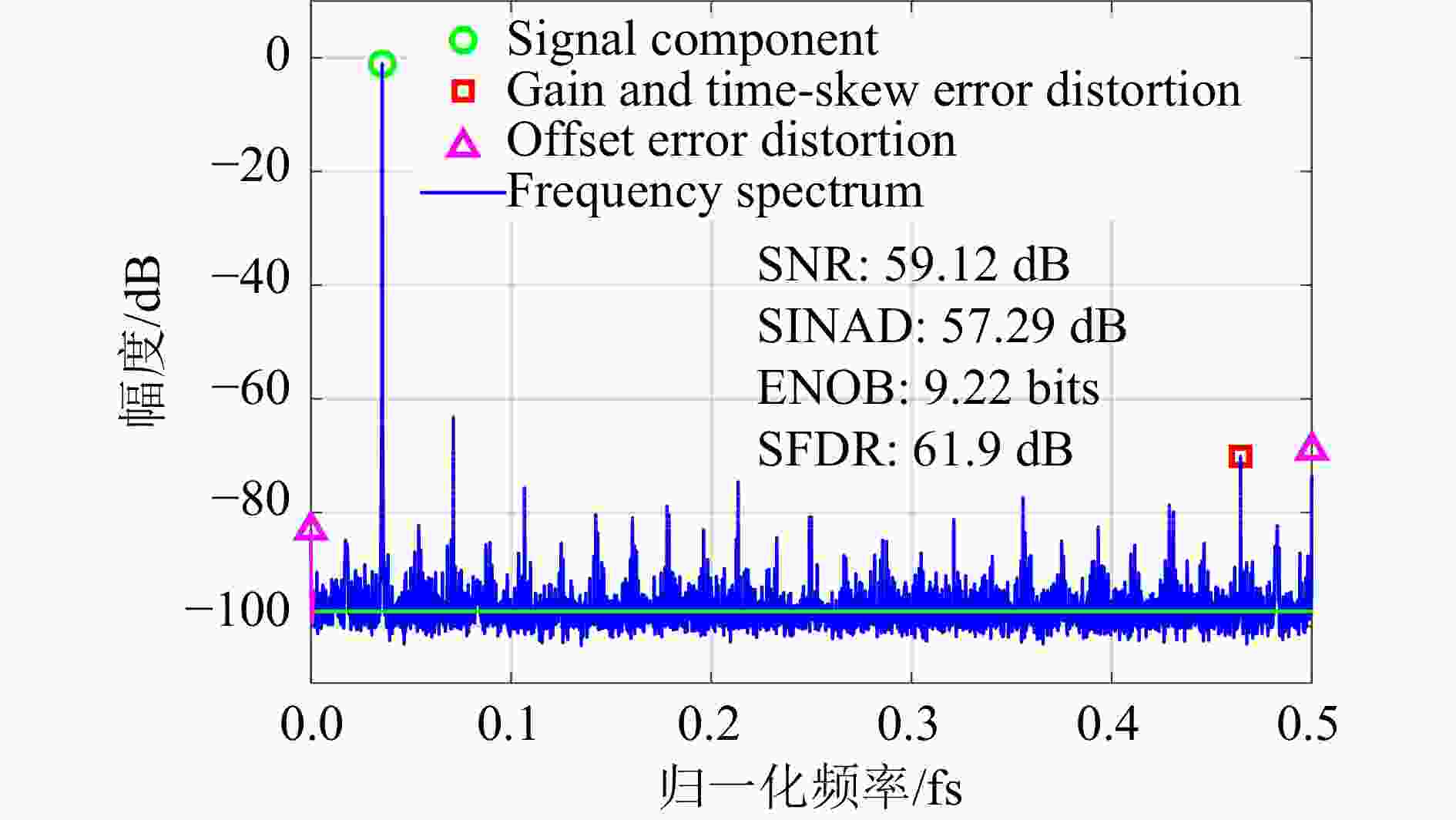

在输入177 MHz的单一频率正弦波时,ADC1和ADC2采样结果的频谱分别如图13和图14所示,2个ADC并行交替采样结果的频谱如图15所示。从图中可以看到,由于失配误差的存在,并行交替采样结果的频谱上会出现伪峰,图中标注出了伪峰的位置。在失配误差的影响下,系统动态性能明显下降,相对于ADC1,SNR下降17 dB,SINAD下降15 dB,SFDR下降21 dB,ENOB下降2.5 bits,这也说明了失配误差修正的重要性与必要性。

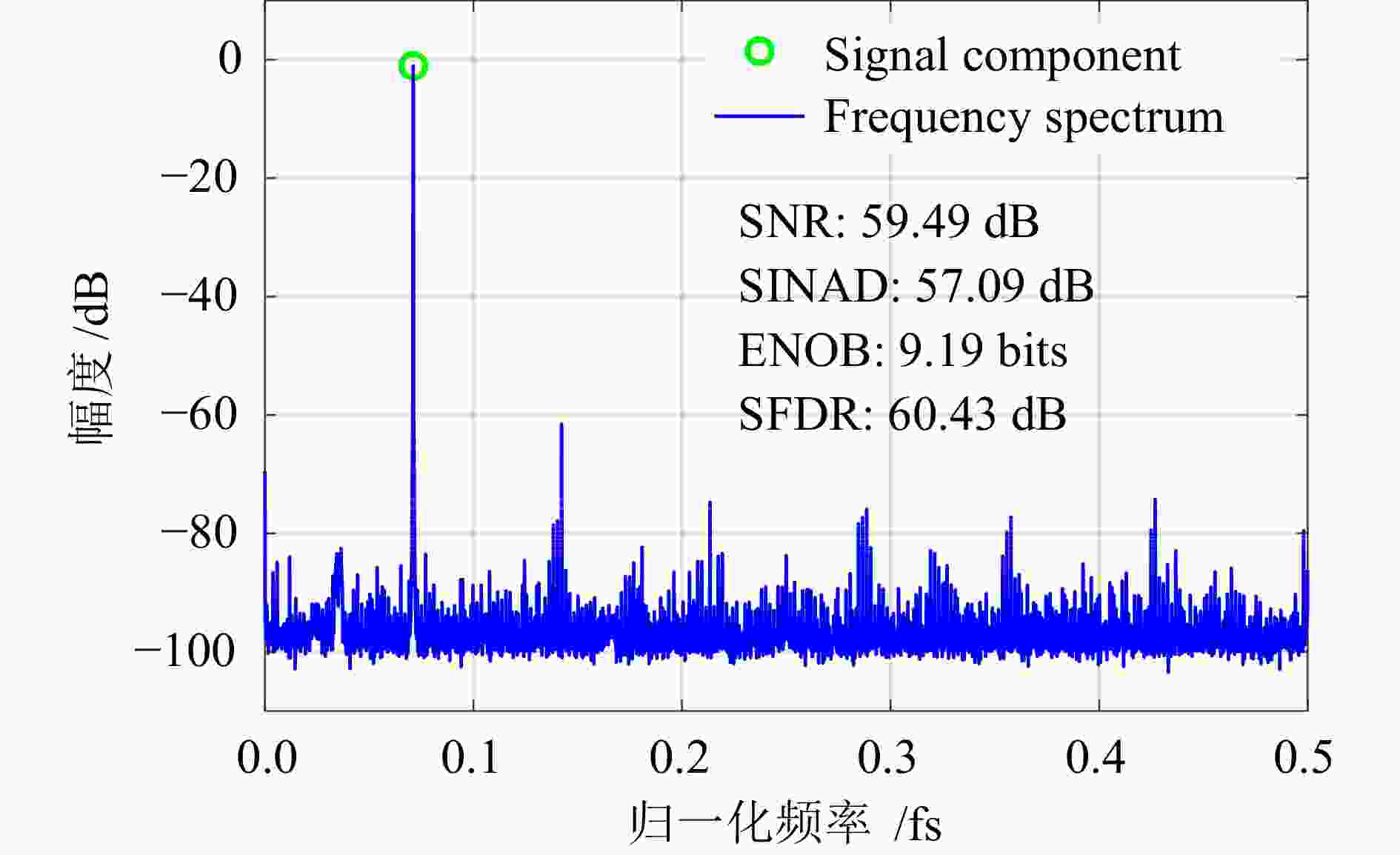

接下来,基于完美重构算法计算FIR滤波器系数,利用此系数对TIADC采样序列进行修正,设定修正滤波器阶数K = 80,修正后序列的频谱如图16所示。对比图15发现,增益误差与相位误差产生的伪峰得到了明显的消减,各项动态性能均得到了明显提升,与单个ADC相当。

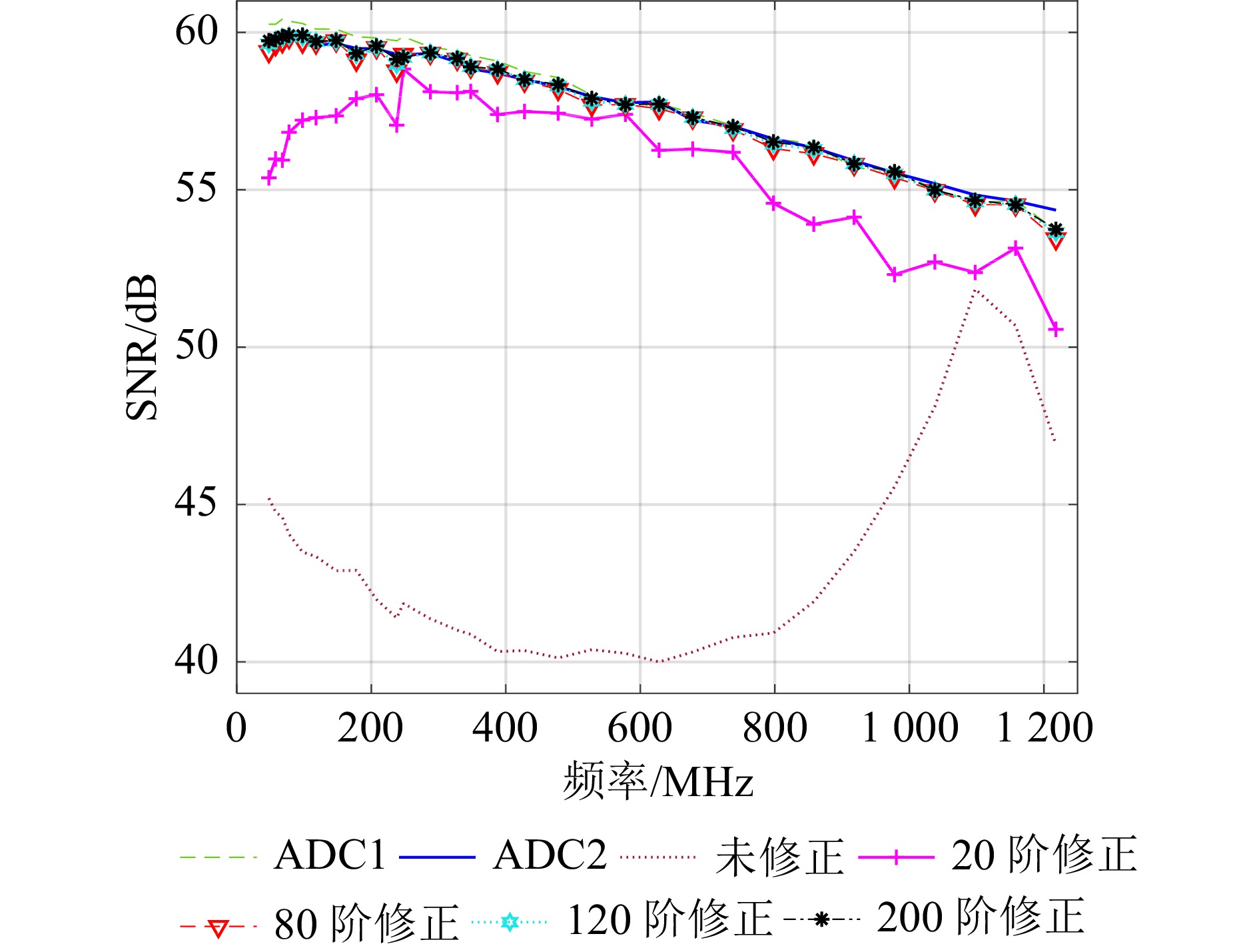

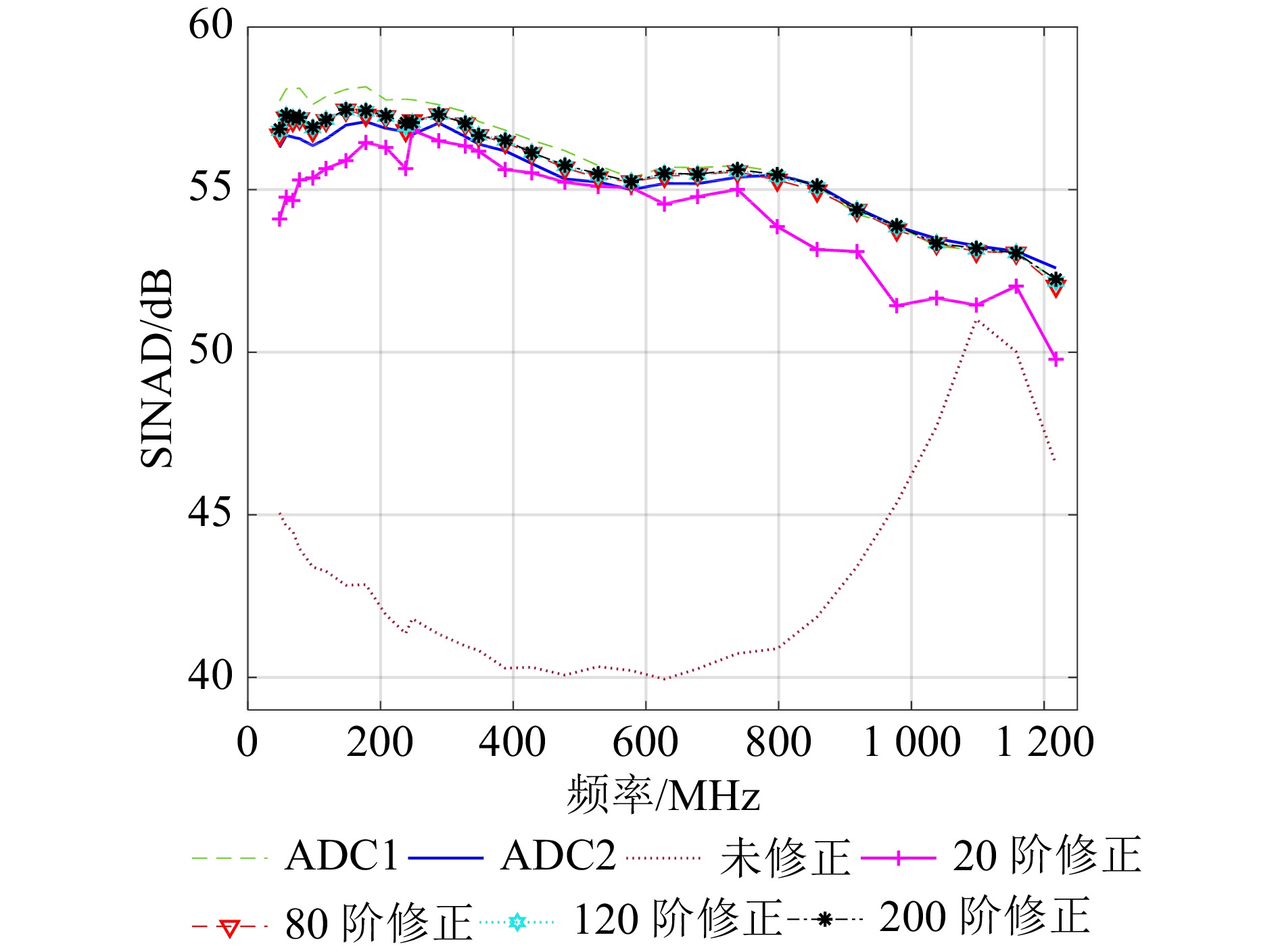

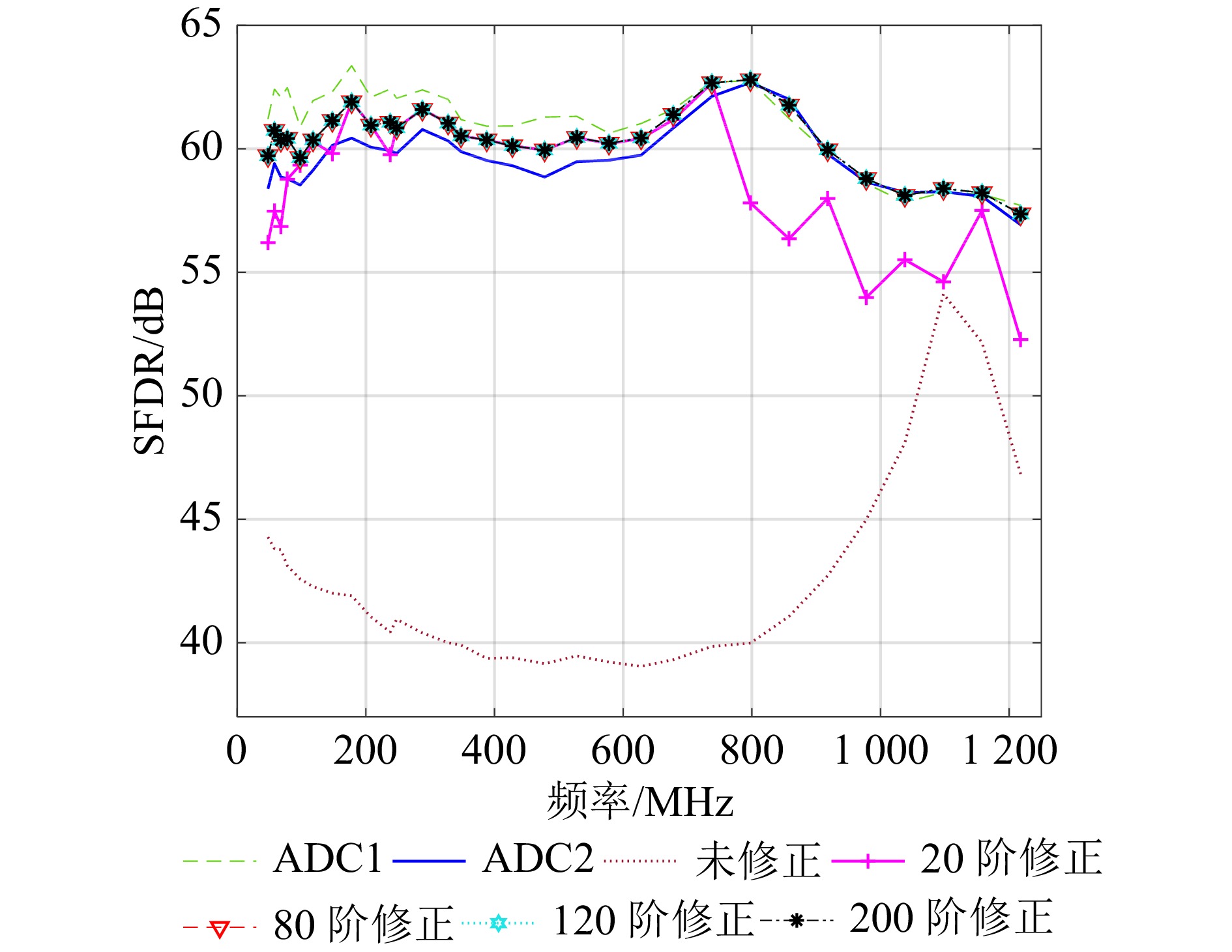

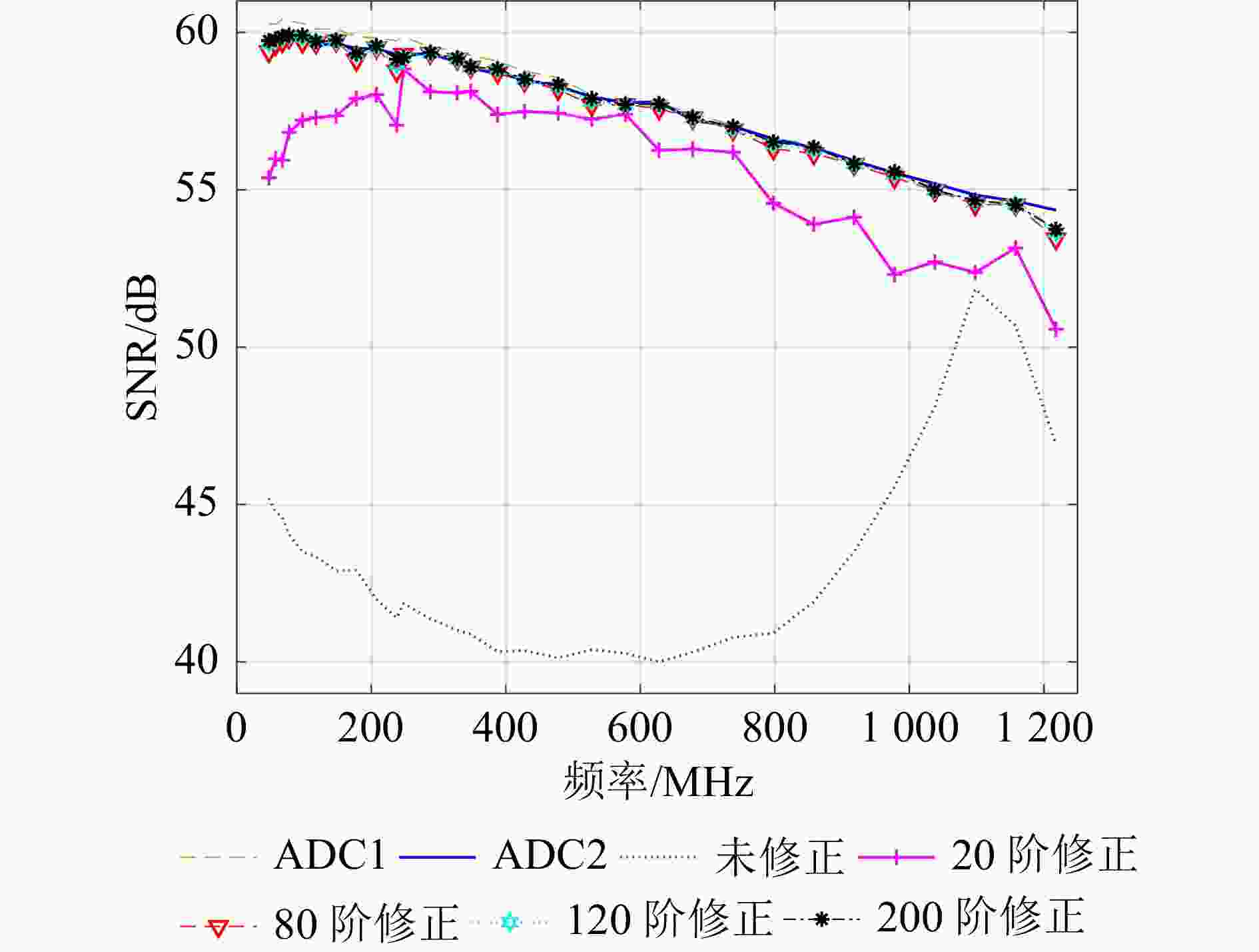

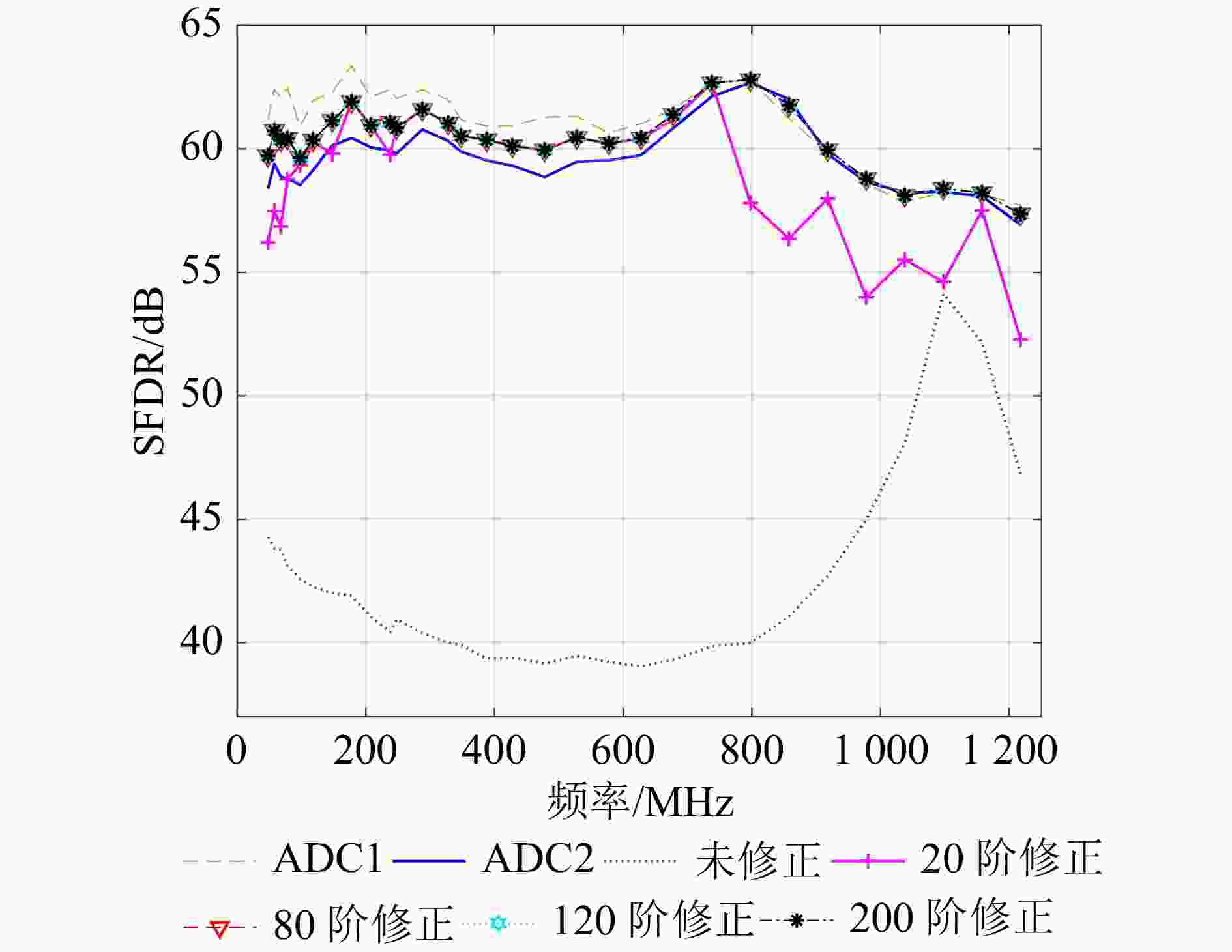

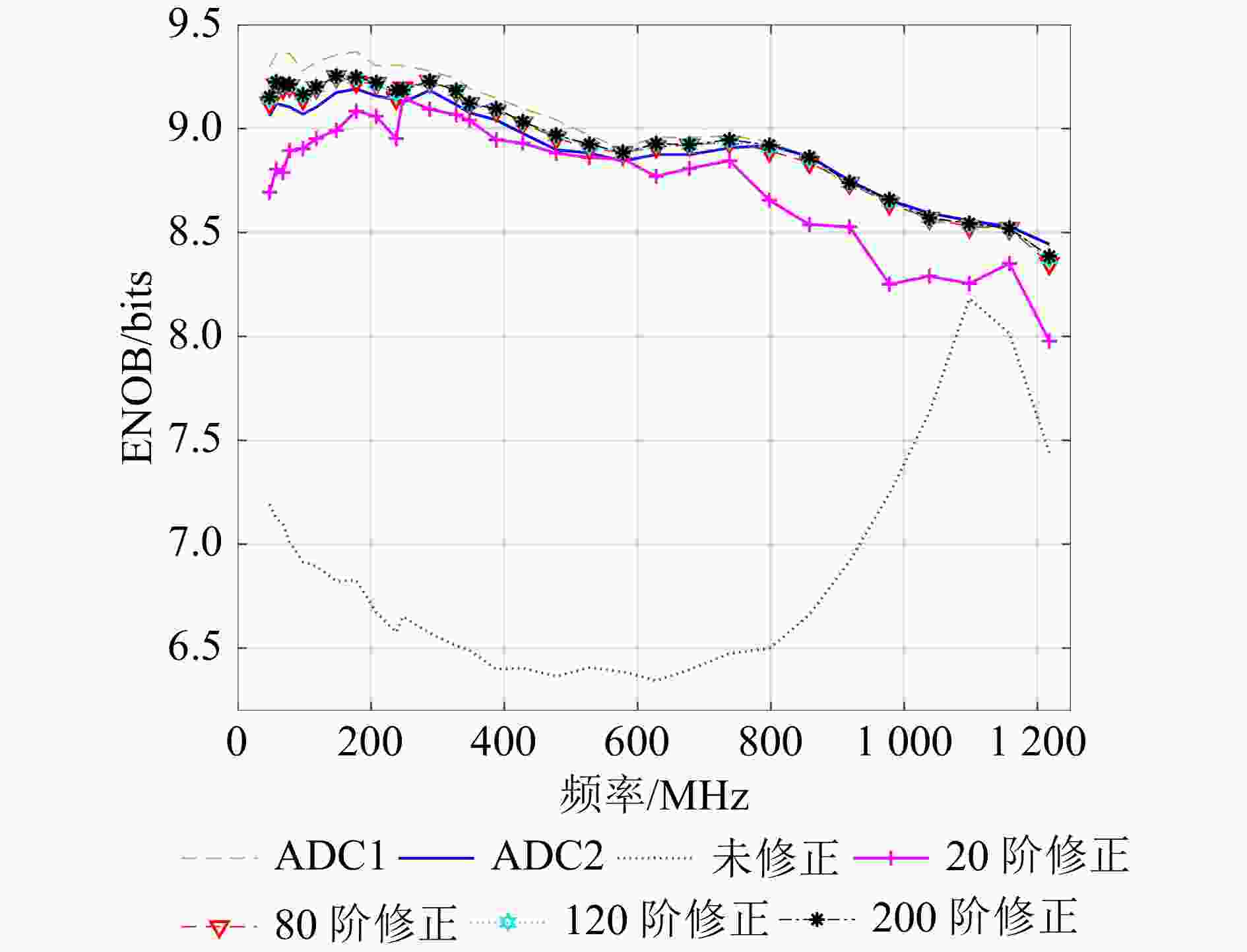

设定不同的滤波器阶数对失配误差进行修正,设定滤波器阶数分别为20阶、80阶、120阶与200阶,ADC1采样结果、ADC2采样结果、原始并行交替采样结果及不同阶数滤波器修正后结果的SNR、SINAD、SFDR、ENOB随频率的变化分别如图17~图20所示。从图中可以看到,各阶数下修正后系统的各项动态性能均得到显著提升。当滤波器阶数为20时,动态性能虽相对于未修正有所提升,但仍未达到单个ADC水平;而更高阶数的滤波器能够达到更好的修正效果,当滤波器阶数为120时,修正后ENOB性能达到9.2 bits@247 MHz,8.9 bits@857 MHz,与单个ADC相当,以上结果说明失配误差的修正对于TIADC系统十分必要,而基于此算法可以实现宽带内的失配误差修正。

-

本工作对TIADC系统进行了一系列测试与性能评估,并基于修正算法对TIADC的失配误差进行了修正。通过测试证明,该系统使用2片国产高速ADC并行交替采样实现了5 Gsps的等效采样率,在未修正时失配误差的存在会使得TIADC系统的动态性能相对于单个ADC明显下降,基于完美重构算法,可实现宽带内失配误差的修正,修正后系统的动态性能得到了明显优化,在120阶滤波器作用下,有效位性能达9.2 bits@247 MHz,8.9 bits@857 MHz,与单片ADC性能相当。

Testing and Evaluation of a Waveform Digitization System Based on TIADC Technique

doi: 10.11804/NuclPhysRev.40.2022102

- Received Date: 2022-09-23

- Rev Recd Date: 2022-10-31

- Available Online: 2024-02-04

- Publish Date: 2023-12-20

Abstract: Time-Interleaved Analog-to-Digital Conversion(TIADC) is one of the most important techniques in the design of high-speed waveform digitization systems, it can multiple the sampling rate of a sampling system. However, there are mismatch errors between different sampling channels, which will make the dynamic performance of a TIADC system significantly lower than that of a single ADC. Therefore, mismatch errors should be corrected in TIADC system design. To evaluate the quality of the system design and promote the next optimization design, it is necessary to conduct scientific performance test and evaluation on the TIADC system. In this work, aiming at the test and evaluation, the performance indexes and test methods of TIADC system are introduced in detail, a series of performance tests of the system are completed, and mismatch errors are corrected based on perfect reconstruction algorithm. The test results show that the system can achieve an equivalent 5 Gsps sampling rate and can realize mismatch error correction in a wide band based on the proposed mismatch error correction method. After correction, the dynamic performance of the TIADC system is significantly enhanced compared with that without correction. For example, the Effective Number of Bits(ENOB) of the proposed system reaches 9.2 bits at 247 MHz, 8.9 bits at 857 MHz, which is equivalent to the performance index of a single ADC.

| Citation: | Yi CAO, Jiajun QIN, Lei ZHAO, Qi AN. Testing and Evaluation of a Waveform Digitization System Based on TIADC Technique[J]. Nuclear Physics Review, 2023, 40(4): 579-588. doi: 10.11804/NuclPhysRev.40.2022102 |

甘公网安备 62010202000723号

甘公网安备 62010202000723号 DownLoad:

DownLoad: